#### UNIVERSITY OF MINNESOTA

This is to certify that I have examined this copy of a doctoral thesis by

#### Haihua Su

and have found that it is complete and satisfactory in all aspects, and that any and all revisions required by the final examining committee have been made.

| Professor Sachin S. Sapatnekar |

|--------------------------------|

| Name of Faculty Advisor        |

| Signature of Faculty Advisor   |

| Date                           |

GRADUATE SCHOOL

# Design and Optimization of Global Interconnect in High Speed VLSI Circuits

# A THESIS SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA

BY

#### HAIHUA SU

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS  $\mbox{FOR THE DEGREE OF} \\ \mbox{DOCTOR OF PHILOSOPHY}$

Sachin S. Sapatnekar, Advisor

JANUARY 2002

## Abstract

This thesis consists of three parts, corresponding to various aspects of global interconnect design issues. The first part deals with the design and optimization of power distribution networks, with special consideration to power grid topology design, wire sizing and decoupling capacitor placement. The second part presents a hybrid mesh/tree clock network construction technique with wire sizing and buffer insertion for performance optimization. Finally, the last part is devoted to a global interconnect congestion reduction technique that simultaneously considers the performance requirements for both signal lines and power grids.

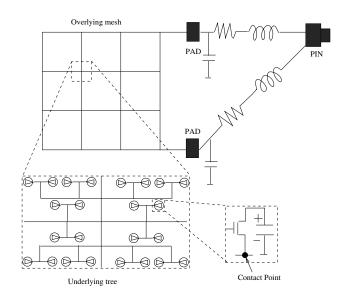

For the design and optimization of power distribution networks, we propose a structured skeleton that is intermediate to the conventional method that uses full meshes which are hard to analyze efficiently, and tree-structured networks, which provide poor performance. As an example, we consider a power/ground (P/G) network structure modeled as an overlying mesh with underlying trees originating from the mesh, which eases the task of analysis with acceptable performance sacrifices. A fast and efficient event-driven P/G network simulator is proposed, which hierarchically simulates the P/G network with an adaptation of PRIMA to handle non-zero initial conditions. This network is then optimized by using wire widening and placing decoupling capacitors (decaps). An adjoint network that incorporates the variable topology of the original P/G network, as elements switch in and out of the network, is constructed to calculate the transient adjoint sensitivity over multiple intervals. The gradients of the most critical node with respect to each wire width and decap are used by a sensitivity-based heuristic optimizer that minimizes a weighted sum of the wire and the decap area.

For ASIC-like circuits, the addition of decoupling capacitances is arguably the most powerful degree of freedom that a designer has for power-grid noise abatement

and is becoming more important as technology scales. We propose and demonstrate an algorithm for the automated placement and sizing of decaps and show that this allows power grid noise to be significantly reduced with little change in the total chip area.

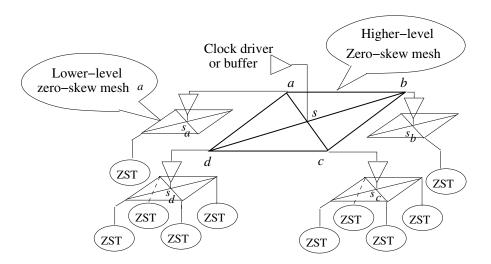

Next, the idea of a hybrid mesh/tree structure is applied to the design of clock distribution networks. We hierarchically construct a hybrid mesh/tree clock network structure consisting of overlying zero-skew clock meshes, with underlying zero-skew clock trees originating from the mesh nodes. We propose a mesh construction procedure, which guarantees zero skew under the Elmore delay model, using a simple and efficient linear programming formulation. Buffers are inserted to reduce the transition time (or rise time). As a post-processing step, wire width optimization under an accurate higher-order delay metric is performed to further minimize the transition time and propagation delay/skew. The hybrid mesh/tree construction scheme provides a smaller propagation delay and transition time than a comparable clock tree. The tolerance to process variations is also shown to be much better than a clock tree. Results of comparing various hybrid structures have also been studied.

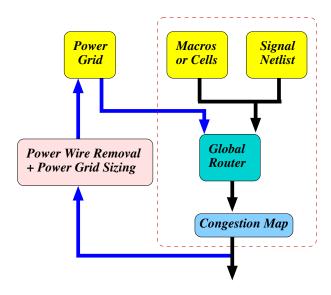

Finally, a global wire design methodology that simultaneously considers the performance needs for both signal lines and power grids under congestion considerations is presented. An iterative procedure is employed in which the global routing is performed according to a congestion map that includes the resource utilization of the power grid, followed by a step in which the power grid is adjusted to relax the congestion in crowded regions. This adjustment is in the form of wire removal in noncritical regions, followed by a wire sizing step that overcomes the effects of wire removal. The overall routability is demonstrated to be significantly improved while the power grid noise is maintained within a specified constraint.

# Acknowledgment

First of all, I would like to thank my advisor, Professor Sachin Sapatnekar, for the invaluable guidance and patient help he has given to me throughout my Ph.D. study and research. I sincerely appreciate his persistent encouragement all these years, especially when I met difficulties. His broad knowledge and keen perception into various cutting-edge research directions in VLSI CAD have led me right into the door of this area, which is beneficial to my research and this dissertation, and of course, will be profitable to my future career. What also impressed me is his enthusiastic pursuit towards the truth, which has been and will be stimulating me throughout my life.

I would also like to thank my committee members, Professors Eugene Shragowitz, Professor Gerald Sobelman and Professor Kia Bazargan for their helpful advice.

I am grateful to Dr. Sani Nassif, the mentor of my internship at the IBM Austin Research Lab, who has not only provided the precious help and guidance to this research, but has also brought me into the most fascinating world of industry CAD tool implementation as well. I would like to acknowledge Dr. Jiang Hu at IBM Microelectronics and Kaushik Gala at Motorola, both previous graduate students from our group, for their collaborative work with me. I also thank Dr. Charles Alpert and Dr. Frank Liu at IBM Austin Research Lab, Dr. Chandu Visweswariah at IBM T. J. Watson Research Center and Professor Duncan M. H. Walker of Texas A&M University for their helpful discussions.

I owe many thanks to fellow graduate students for helping me at different times and making my life in Minneapolis pleasant and fruitful: Min Zhao, Jiang Hu, Kaushik Gala, Jatuchai Pangjun, Mahesh Ketkar, Suresh Raman, Shrirang Karandikar, Raza ul Mustafa, Haitian Hu, Rupesh Shelar, Cheng Wan, Venkatesan Rajappan, Tianpei Zhang, Yong Zhan and Brent Goplen.

I am grateful to National Science Foundation, Semiconductor Research Cooperation for funding parts of my research, and IEEE, ACM and the University of Minnesota for providing financial support to attend conferences, and to the IBM Austin Research Lab for providing me with the opportunity to work as a co-op.

Finally I would like to thank my husband Xiaolue Lai for his encouragement and support throughout these years, which makes my life much more meaningful and enjoyable. And lastly, I am very grateful to my parents for their illuminating guidance ever since I was a child. I would like to give my special thanks, from my deepest heart, to my mother for all her sacrifice and hardship of raising me up and supporting me toward higher education and new challenges ever.

# Contents

| 1 | Intr           | Introduction                           |    |  |  |  |

|---|----------------|----------------------------------------|----|--|--|--|

|   | 1.1            | Technology Trends and Research Goal    | 1  |  |  |  |

|   | 1.2            | Contributions                          | 5  |  |  |  |

| 2 | $\mathbf{Pre}$ | liminaries                             | 8  |  |  |  |

|   | 2.1            | Supply and Clock Network Modeling      | 8  |  |  |  |

|   |                | 2.1.1 Supply Network Modeling          | 8  |  |  |  |

|   |                | 2.1.2 Clock Network Modeling           | 9  |  |  |  |

|   | 2.2            | Circuit Analysis Basics                | 10 |  |  |  |

|   | 2.3            | Interconnect Performance Metrics       | 11 |  |  |  |

|   |                | 2.3.1 Power Grid Noise Metric          | 11 |  |  |  |

|   |                | 2.3.2 Delay modeling                   | 12 |  |  |  |

|   | 2.4            | Transient Adjoint Sensitivity Analysis | 13 |  |  |  |

|   | 2.5            | Global Wire Congestion Measurement     | 15 |  |  |  |

| 3 | Fast Analysis and Optimization of Structured Power/Ground Net- |         |                                                                 |    |  |  |

|---|----------------------------------------------------------------|---------|-----------------------------------------------------------------|----|--|--|

|   | wor                                                            | ks      |                                                                 | 16 |  |  |

|   | 3.1                                                            | Introd  | luction                                                         | 16 |  |  |

|   |                                                                | 3.1.1   | Previous Work                                                   | 17 |  |  |

|   |                                                                | 3.1.2   | Motivation for Hybrid Topology                                  | 17 |  |  |

|   |                                                                | 3.1.3   | Contributions                                                   | 18 |  |  |

|   | 3.2                                                            | Hiera   | rchical Analysis of the P/G Network Incorporating Non-zero Ini- |    |  |  |

|   |                                                                | tial C  | onditions                                                       | 22 |  |  |

|   |                                                                | 3.2.1   | Reduction of the Trees                                          | 23 |  |  |

|   |                                                                | 3.2.2   | Solving the Mesh                                                | 23 |  |  |

|   |                                                                | 3.2.3   | Propagating Waveforms Down the Trees                            | 24 |  |  |

|   | 3.3                                                            | Adjoir  | nt Sensitivity Computation Over Multiple Intervals              | 26 |  |  |

|   |                                                                | 3.3.1   | Sensitivity with Respect to Capacitors                          | 27 |  |  |

|   |                                                                | 3.3.2   | Sensitivity with Respect to Resistors and Inductors             | 29 |  |  |

|   |                                                                | 3.3.3   | Closed-form Transient Sensitivity Formula                       | 30 |  |  |

|   | 3.4                                                            | Heuris  | stic Optimization                                               | 32 |  |  |

|   | 3.5                                                            | Exper   | rimental Results                                                | 35 |  |  |

|   | 3.6                                                            | Concl   | usion                                                           | 37 |  |  |

| 4 | Opt                                                            | timal l | Decoupling Capacitor Sizing and Placement for Standard          | l  |  |  |

|   | Cel                                                            | l Layo  | ${f uts}$                                                       | 39 |  |  |

|   | 4.1                                                            | Introd  | duction and Motivation                                          | 39 |  |  |

|   | 4.1.1 Motivation                                               |         |                                                                 |    |  |  |

|   |     | 4.1.2                                                        | Previous Work                                                 | 42                              |

|---|-----|--------------------------------------------------------------|---------------------------------------------------------------|---------------------------------|

|   |     | 4.1.3                                                        | Contributions                                                 | 43                              |

|   | 4.2 | Power                                                        | Supply Noise and Sensitivity Analysis                         | 44                              |

|   |     | 4.2.1                                                        | Noise Analysis                                                | 44                              |

|   |     | 4.2.2                                                        | Integral Sensitivity Computation                              | 45                              |

|   | 4.3 | Optim                                                        | nization and Placement                                        | 48                              |

|   |     | 4.3.1                                                        | Problem Formulation                                           | 48                              |

|   |     | 4.3.2                                                        | Optimization and Placement Scheme                             | 49                              |

|   | 4.4 | Exper                                                        | imental results                                               | 50                              |

|   | 4.5 | Concl                                                        | usion                                                         | 54                              |

| 5 | Hyl | orid Cl                                                      | lock Distribution Network Construction                        | 55                              |

|   |     |                                                              |                                                               |                                 |

|   | 5.1 | Introd                                                       | uction                                                        | 55                              |

|   | ·   | Introd                                                       |                                                               | 55<br>55                        |

|   | ·   |                                                              | uction                                                        |                                 |

|   | ·   | 5.1.1                                                        | uction                                                        | 55                              |

|   | ·   | 5.1.1<br>5.1.2<br>5.1.3                                      | uction          Clock Design Objective          Previous Work | 55<br>56                        |

|   | 5.1 | 5.1.1<br>5.1.2<br>5.1.3<br>Linear                            | Clock Design Objective                                        | 55<br>56<br>56                  |

|   | 5.1 | 5.1.1<br>5.1.2<br>5.1.3<br>Linear                            | Clock Design Objective                                        | 55<br>56<br>56<br>59            |

|   | 5.1 | 5.1.1<br>5.1.2<br>5.1.3<br>Linear<br>5.2.1                   | Clock Design Objective                                        | 55<br>56<br>56<br>59            |

|   | 5.1 | 5.1.1<br>5.1.2<br>5.1.3<br>Linear<br>5.2.1<br>5.2.2          | Clock Design Objective                                        | 555<br>566<br>569<br>599<br>633 |

|   | 5.1 | 5.1.1<br>5.1.2<br>5.1.3<br>Linear<br>5.2.1<br>5.2.2<br>5.2.3 | Clock Design Objective                                        | 555<br>566<br>569<br>599<br>633 |

|   | 5.3 | Fast A  | Analysis and Heuristic Optimization                        | 68  |

|---|-----|---------|------------------------------------------------------------|-----|

|   |     | 5.3.1   | Fast Higher-order Delay Calculation                        | 68  |

|   |     | 5.3.2   | Calculation of Sensitivities                               | 69  |

|   |     | 5.3.3   | Heuristic Optimization Procedure                           | 70  |

|   | 5.4 | Exper   | imental Results                                            | 72  |

|   | 5.5 | Concl   | usion                                                      | 79  |

| 6 | Cor | ıgestio | n-driven Codesign of Power and Signal Networks             | 80  |

|   | 6.1 | Introd  | luction                                                    | 80  |

|   |     | 6.1.1   | Motivation for the Codesign of Signal and Power Wires      | 80  |

|   |     | 6.1.2   | Previous Work on Signal Wires and Power Wires Individually | 82  |

|   |     | 6.1.3   | Contributions                                              | 83  |

|   | 6.2 | Power   | Grid-aware Signal Routing                                  | 84  |

|   |     | 6.2.1   | Power Grid-aware Congestion Estimation                     | 84  |

|   |     | 6.2.2   | Congestion-driven Global Routing                           | 86  |

|   | 6.3 | Power   | Supply Noise Analysis                                      | 87  |

|   | 6.4 | Power   | Grid Design Scheme                                         | 88  |

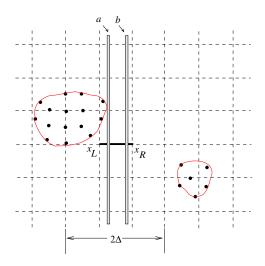

|   |     | 6.4.1   | Power Grid Wire Removal Heuristic                          | 89  |

|   |     | 6.4.2   | Power Grid Sizing                                          | 92  |

|   | 6.5 | Overa   | ll Flow of the Algorithm                                   | 94  |

|   |     | 6.5.1   | Overall Flow                                               | 94  |

|   |     | 6.5.2   | Complexity Discussions                                     | 96  |

|   | 6.6 | Exper   | imental Results                                            | 96  |

|   | 6.7 | Concl   | usion                                                      | 101 |

7 Conclusions 103

# List of Figures

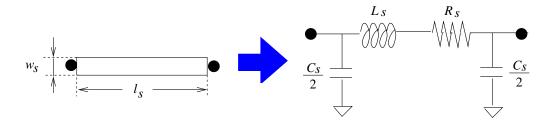

| 2.1 | RLC $\pi$ -model of wire segment                                              | 9  |

|-----|-------------------------------------------------------------------------------|----|

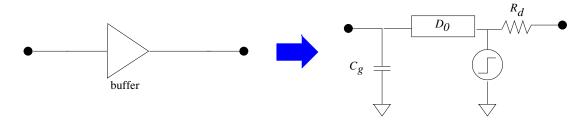

| 2.2 | Linear buffer modeling                                                        | 10 |

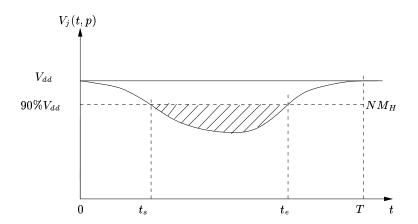

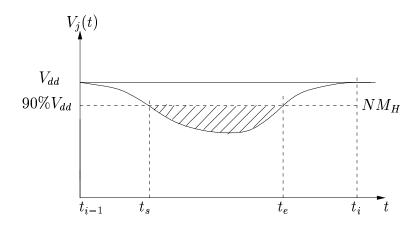

| 2.3 | Illustration of the voltage droop at a given node in the $V_{dd}$ power grid. |    |

|     | The area of the shaded region corresponds to the integral $z$ at that node.   | 12 |

| 2.4 | A Circuit $N$ and its adjoint circuit $\eta$                                  | 13 |

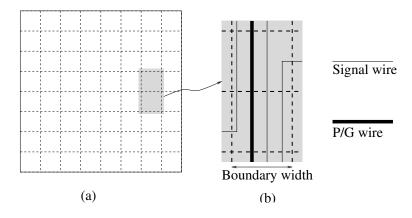

| 2.5 | Wire congestion estimation based on tessellation on a chip                    | 15 |

| 3.1 | A structured P/G bus topology                                                 | 19 |

| 3.2 | Switching events at a node in a P/G network                                   | 19 |

| 3.3 | Voltage droop of node $j$ in a power network during event $i-1$ and $i$ .     | 20 |

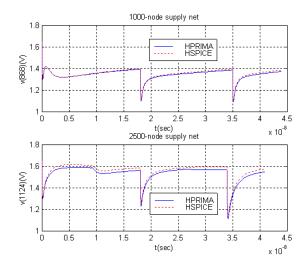

| 3.4 | Simulation results on a 1000-node and a 2500-node supply network.             |    |

|     | The reduced orders for the two networks are 13 and 15, respectively.          |    |

|     | HPRIMA stands for our Hierarchical PRIMA simulator. $V_{dd} = 1.65V$ .        | 36 |

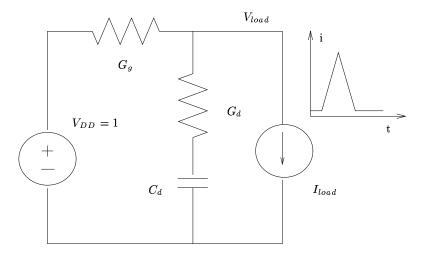

| 4.1 | A canonical and approximate circuit representation of a power network.        | 41 |

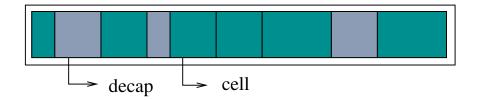

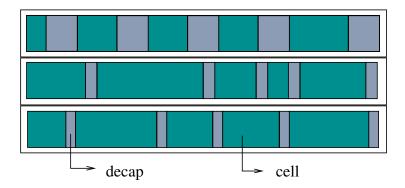

| 4.2 | One row of cells in a standard cell layout showing decap locations            | 43 |

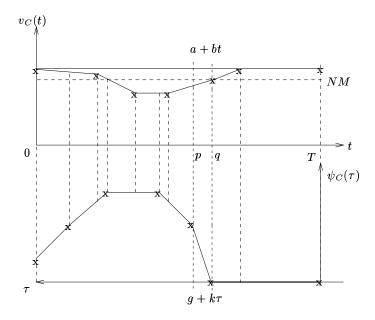

| 4.3 | Compressed piecewise-linear waveforms for the original and adjoint            |    |

|     | networks.                                                                     | 47 |

| 4.4 | Illustration of the initial equal distribution of decaps                      | 49  |

|-----|-------------------------------------------------------------------------------|-----|

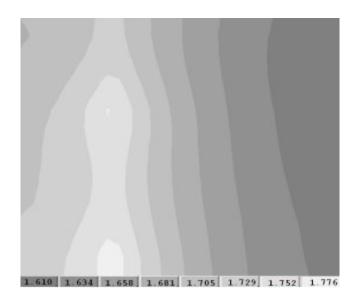

| 4.5 | The original voltage droop contour of the $Vdd$ plane                         | 52  |

| 4.6 | The original voltage droop contour of the ground plane                        | 52  |

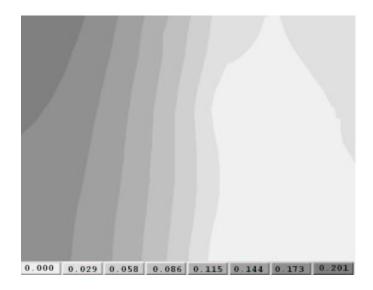

| 4.7 | Results of the decap placement algorithm on chip2. The dark regions           |     |

|     | represent the standard cells, and the light regions are the decaps. $$ . $$ . | 53  |

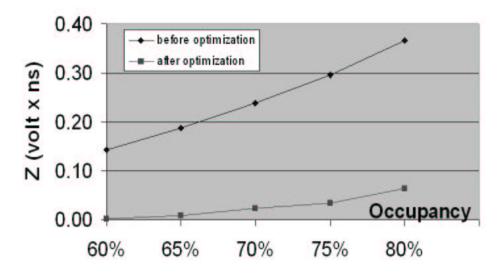

| 4.8 | Variation of the noise metric with the occupancy ratio                        | 53  |

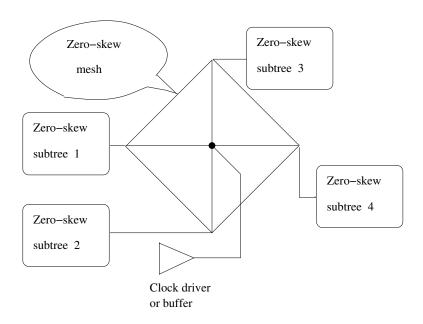

| 5.1 | A clock network as a mesh/tree structure                                      | 57  |

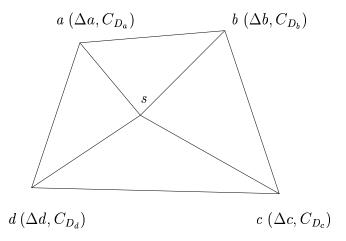

| 5.2 | One-level mesh with underlying trees                                          | 60  |

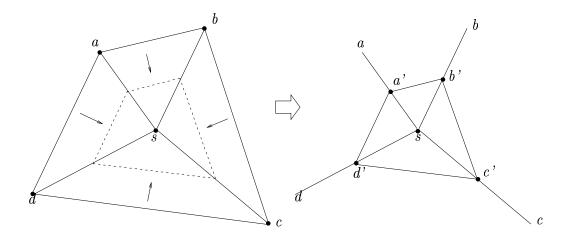

| 5.3 | Mesh "shrinking" heuristic.                                                   | 66  |

| 5.4 | Two-level mesh with underlying trees. For simplicity, only some of the        |     |

|     | sixteen zero skew trees are shown                                             | 68  |

| 6.1 | Congestion-driven power grid design and global routing                        | 83  |

| 6.2 | Wire congestion estimation based on tessellation on a chip                    | 85  |

| 6.3 | Illustration of the criticality of power wires                                | 90  |

| 6.4 | Heuristic power wire removal                                                  | 92  |

| 6.5 | Power grid sizing procedure                                                   | 94  |

| 6.6 | Congestion map after the initial routing                                      | 101 |

| 6.7 | Voltage droop contour on the ground plane                                     | 101 |

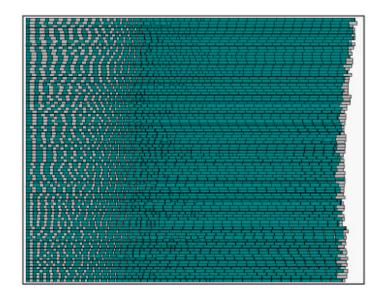

| 6.8 | Optimal M3 and M4 power grid of ac3                                           | 102 |

# List of Tables

| 1.1 | Trends in IC technology parameters                                    | 2  |

|-----|-----------------------------------------------------------------------|----|

| 3.1 | Runtime comparisons with HSPICE                                       | 37 |

| 3.2 | Optimization results                                                  | 38 |

| 3.3 | Topology comparison                                                   | 38 |

| 4.1 | IC technology parameters                                              | 40 |

| 4.2 | Optimization results                                                  | 51 |

| 5.1 | Comparison between structures of clock nets                           | 73 |

| 5.2 | Mesh wire elongation ratio                                            | 74 |

| 5.3 | Wire width optimization results                                       | 75 |

| 5.4 | Process variation results                                             | 76 |

| 5.5 | Hybrid clock networks after heuristic transition time improvement     | 77 |

| 5.6 | Comparison with the IBM structure                                     | 78 |

| 6.1 | Test circuit parameters.                                              | 97 |

| 6.2 | A comparison of the congestion improvement after global routing using |    |

|     | the conventional approach and our new method                          | 98 |

| 6.3 | Optimal power grid results                                      | 96  |

|-----|-----------------------------------------------------------------|-----|

| 6.4 | CPU time statistics and number of iterations for the benchmarks | 100 |

# Chapter 1

## Introduction

## 1.1 Technology Trends and Research Goal

Moore's Law [1] defined the technology scaling trends for the past thirty years and it is expected that the exponential scaling will continue for at least another 10 to 14 years as projected in the International Technology Roadmap for Semiconductors (ITRS'01) [2], summarized in Table 1.1. As a result, over 2.8 billion transistors will be integrated on a single-chip with a clock frequency of 29GHz in the 22nm technology by Year 2016.

It can be seen from Table 1.1 that the trend for high performance integrated circuits is towards ever higher operating frequency, lower power supply voltages and higher power dissipation. The increased power consumption is driven by higher operating frequency and the higher overall capacitance and resistance of larger chips with more on-chip functions [2]. Global interconnect, which distributes the clock and other signals and providing power/ground to the various circuit functions on a chip, has become critical in determining system performance and reliability.

This work aims at the optimal design of various global wires. In specific, it

| Year | Tech | Num              | Num         | f     | $V_{dd}$ | Size     | Power |

|------|------|------------------|-------------|-------|----------|----------|-------|

|      | Node | of               | Wire        | (MHz) | (V)      | $(mm^2)$ | (W)   |

|      | (nm) | Tran             | Level       |       |          |          |       |

| 2001 | 130  | 89M              | 7           | 1684  | 1.1      | 310      | 130   |

| 2002 | 115  | 112M             | $7 \sim 8$  | 2317  | 1.0      | 310      | 140   |

| 2003 | 100  | 142M             | 8           | 3088  | 1.0      | 310      | 150   |

| 2004 | 90   | 178M             | 8           | 3990  | 1.0      | 310      | 160   |

| 2005 | 80   | $225\mathrm{M}$  | $8 \sim 9$  | 5173  | 0.9      | 310      | 170   |

| 2006 | 70   | 283M             | 9           | 5631  | 0.9      | 310      | 180   |

| 2007 | 65   | 357M             | 9           | 6739  | 0.7      | 310      | 190   |

| 2010 | 45   | 714M             | $9 \sim 10$ | 11511 | 0.6      | 310      | 218   |

| 2013 | 32   | $1427\mathrm{M}$ | $9 \sim 10$ | 19348 | 0.5      | 310      | 251   |

| 2016 | 22   | 2854M            | 10          | 28751 | 0.4      | 310      | 288   |

Table 1.1: Trends in IC technology parameters.

addresses both the separate design of power and clock distribution networks, as well as the codesign of power and signal networks.

The power distribution network (also known as supply network) provides the  $V_{dd}$  and ground signals throughout a chip. These signals are among the most important signals to control reliably since supply voltage variations can lead not only to problems related to spurious transitions in some cases, particularly when dynamic logic is used, but also to delay variations [3] and timing unpredictability. In deep sub-micron designs, power supply noise is among the major reasons that affect the circuit functionality. The problems in power grid are: the voltage droop due to current flow in the network, ground bounce due to inductive effects, and possible electromigration effects due to excessive current densities. Even if a reliable supply is provided at an input pin of a chip, it can deteriorate significantly within the chip due to the fact that the conductors that transmit these signals throughout the chip are electrically

imperfect.

Various techniques including topology optimization, wire sizing optimization and decoupling capacitor placement have been applied to solve the above problems in supply networks. In this thesis, we study power grid design problems in the following aspects: topology design, fast analysis methods, wire sizing and automatic decoupling capacitor optimization/placement schemes.

Clock distribution has become an increasingly challenging problem for VLSI designs, and careful design of clock networks is essential in high-performance circuits.

The timing metrics for a clock distribution network include:

- Skew, defined as the maximum difference of the delays from the clock driver or buffer to the clock pins or buffer input capacitances.

- Propagation delay, defined as the maximum 50% delay from the clock driver or buffer to the clock pins or buffer input capacitances.

- Transition time (or slew rate or rise time), defined as the time it takes for the step/ramp response waveform to change from 10% to 90% of the  $V_{dd}$  level.

In addition, the tolerance of clock skew to process variations and the skew sensitivity to loading conditions are also very important factors to determine the performance of clock networks.

The most common objectives of clock network design are to ensure near-zero skew, sharp transition times, small propagation delays and the optimal use of routing resources. Various clock network design techniques include topology design, wire sizing optimization and buffer insertion. In [4], different clock network topologies are reviewed and they drew a conclusion that each of these topologies have both advantages and disadvantages that should be considered for a high speed design and

none of these solutions is ideal in itself, which motivates designs of hybrid clock distribution structures that marry the positive attributes of the various techniques. In this thesis, we construct our own zero-skew hybrid clock network and provide fast and accurate analysis and performance optimization technique for such a structure.

In high-performance integrated circuits, signal wires and power wires compete for routing resources. As the number and criticality of global signal wires becomes more dominant, there is a strong need for a unified approach to the design of signal wires and power grids, with an integrated approach to routing resource management. In this thesis, we provide a solution to this problem and present our congestion-driven design flow to perform a concurrent optimization of the power grid along with signal wires under routing congestion constraints.

#### 1.2 Contributions

The major contributions of this thesis are:

- We propose a hybrid structure that is intermediate to full meshes and pure trees to benefit from the advantages of both structures. We apply such a structure to both the design of supply networks and clock distribution networks. In specific, we study a power/ground (P/G) network structure modeled as an overlying mesh with underlying trees originating from the mesh and a clock network structure with overlying zero-skew mesh driving underlying zero-skew buffered trees. For P/G networks, our proposed structure is amenable to fast analysis, while also maintaining the performance by using mesh structures in the upper level. Experimental results for clock networks show that the hybrid mesh/tree construction scheme can provide smaller propagation delay and transition time than a comparable clock tree. The tolerance to process variations is much better than a clock tree.

- For the hybrid-structured supply network, we present an analysis/sensitivity calculation/heuristic optimization procedure to design reliable power distribution networks for ASIC designs, where fast turnaround time of the design is a major criterion, and ease of analysis of the P/G network with an acceptable performance hit can greatly ease the task of P/G network optimization. For such a structure, we first develop a fast and efficient event-driven P/G network simulator (HPRIMA) that hierarchically simulates the P/G network with an adaptation of PRIMA [5] to handle non-zero initial conditions. Then, we extend the traditional adjoint sensitivity analysis technique appropriatly over multiple switching intervals to deal with the variant topology of the P/G network. The sensitivity computation is coupled with our efficient PRIMA-based order reduction approach so that it can handle large-scale P/G circuits. A

closed-form transient sensitivity expression is provided for a PRIMA approximation of a given order. The TILOS-like [6] heuristic wire width optimization is performed according to the gradients calculated through the adjoint sensitivity analysis. We have successfully extended this procedure to include the optimization of decoupling capacitors.

- We propose and demonstrate an algorithm for the automated placement and sizing of decaps for standard cell layouts. In this work, a compressed piecewise linear voltage waveform for every node in the power grid circuit is stored to reduce the amount of memory to be used. Thereafter, the complexity of the convolution computation in the adjoint sensitivity analysis has been significantly reduced. Experimental results show that power grid noise can be significantly reduced after a judicious optimization of decap placement, with little change of the total chip area.

- We develop a novel technique that describes how some classes of meshes can be constructed very easily for zero skew using a simple linear-programming based formulation. This method can be extended very easily to build clock trees with prespecified nonzero skews for cases when deliberate skews are used in the clock network for cycle borrowing [7]. While the first-order Elmore Delay is used in this technique to build the initial zero-skew mesh/tree structure, for accurate analysis of delays and skews and further optimization of the constructed clock network to some target transition time and skews, we extend our hierarchical HPRIMA simulator to analyze the step response of every clock pin. The reduced order modeling approach based on HPRIMA is also employed in calculating the adjoint sensitivities of delays, as well as of skew and transition time with respect to all the wire widths to guide our heuristic wire width optimization for meeting more stringent skew and transition time constraints.

• We perform a concurrent optimization of the power grid along with signal wires under routing congestion constraints. By adding a feedback loop into the conventional global routing flow, we can alter the pre-designed power grid according to the congestion information and re-route congested signal nets using updated routing resources. The power grid adjustments consist of wire removal from the grid in congested regions, and sizing of the power grid to compensate for this removal. Our approach incorporates a tight coupling between power grid adjustments and the routing of signal wires to exploit the altered congestions that result from these adjustments, and aims to solve problems with severe congestion constraints where conventional techniques are inadequate. Experimental results show that the overall routability can be significantly improved while the power grid noise is maintained within the voltage droop constraint.

Parts of this research have been published in [8–13].

# Chapter 2

## **Preliminaries**

## 2.1 Supply and Clock Network Modeling

#### 2.1.1 Supply Network Modeling

The following supply network model has been widely used in industry [14, 15].

- The power distribution network (grid) is modeled as a resistive mesh.

- The cells are modeled as time-varying current sources connected between power and ground.

- The decoupling capacitors are modeled as single lumped capacitors connected between power and ground.

- The top-level metal is connected to a package modeled as an inductance connected to an ideal constant voltage source.

- . We use the above model for the work of decoupling capacitor optimization and the work of congestion-driven power and signal networks because both are industry-

supported projects aiming to solve problems in current technologies where the inductance is dominated by pin inductances.

Figure 2.1: RLC  $\pi$ -model of wire segment.

For more accurate analysis, a slightly complicated interconnect model for the P/G network is used. In this model, each wire in the power grid is represented as a set of connected segments under the  $\pi$ -model (shown in Figure 2.1), with each segment modeled using lumped RLC parameters given by

$$R_s = \rho l_s / w_s$$

$$C_s = (\beta w_s + \alpha) l_s$$

$$L_s = \gamma l_s / w_s$$

(2.1)

where  $l_s$  and  $w_s$  are the length and the width of the segment, and the parameters  $\rho$ ,  $\beta$ ,  $\alpha$  and  $\gamma$  are the sheet resistance per square, sheet capacitance per square, fringing capacitance per unit length and the inductance per square of the metal layer that is being used for routing the P/G network. Package pins are modeled as an RLC branch connected to pads on the mesh.

## 2.1.2 Clock Network Modeling

The clock distribution network is usually modeled as a lumped RC network. The RC parameters can be found out using corresponding equations in Eq. (2.1). Loads at the leaf nodes of the clock distribution network, which are clock pins to the memory

elements (i.e., flip-flops, latches, etc), are modeled as sink capacitances. Clock buffers use the linear model which consists of buffer input capacitance  $(C_g)$ , intrinsic delay  $(D_0)$  and effective resistance  $(R_d)$ . An ideal clock input signal is assumed to be applied to the buffer effective resistance. The buffer model is illustrated in Figure 2.2.

Figure 2.2: Linear buffer modeling.

### 2.2 Circuit Analysis Basics

The behavior of linear circuits can be described in the time domain by a first order differential equation formulated using modified nodal analysis (MNA) [16]:

$$Gx(t) + C\dot{x}(t) = u(t) \tag{2.2}$$

where x is a vector of node voltages and source and inductor currents; G is the conductance matrix; C includes both capacitance inductance terms, and u(t) includes the current and voltage sources.

The MNA equation can be solved using the Backward Euler integration formula [16]:

$$(G + C/h)x(t+h) = u(t+h) + x(t)C/h$$

(2.3)

Where h is the time step for the transient analysis.

The linear circuit system can be transformed in the frequency domain. Applying the Laplace transform, Eq. (2.2) becomes

$$(G+sC)V(s) = J(s) (2.4)$$

Power distribution network is huge in terms of total number of nodes. In both Eq. (2.2) and (2.4), matrices G and C are large such that solving these equations directly will be extremely slow and significant amount of memory will be used. Various research (i.e., [8, 17, 18]), either in the time domain or in the frequency domain, has been performed on seeking techniques to solve these equations fast and efficiently.

#### 2.3 Interconnect Performance Metrics

#### 2.3.1 Power Grid Noise Metric

Maximum voltage droop of a node is defined as the largest voltage droop value along the period of time for simulation. The maximum voltage droop among all nodes in the power grid circuit can give a rough idea about the performance of the power grid. However, such a measurement is very sensitive to the accuracy of circuit analysis and does not take the timings of the voltage violations into account. Hence it would be inefficient to be used as the objective function for optimization purpose.

An efficient noise metric for the performance of every node in a power/ground network is the integral of voltage droop beyond the noise margin:

$$z_{j}(p) = \int_{0}^{T} \max\{NM_{H} - v_{j}(t, p), 0\} dt$$

$$= \int_{t_{s}}^{t_{e}} \{NM_{H} - v_{j}(t, p)\} dt, \qquad (2.5)$$

where p represents the tunable circuit parameters. It is represented by the shaded area in Figure 2.3. This idea was first introduced in [19] and it proves to be an efficient measure for circuit optimization. In our work, this metric has been applied successfully to efficient optimization of power distribution networks.

Figure 2.3: Illustration of the voltage droop at a given node in the  $V_{dd}$  power grid. The area of the shaded region corresponds to the integral z at that node.

#### 2.3.2 Delay modeling

For an RC circuit, Elmore delay [20] has been widely used to estimate interconnect delays because of its simplicity and high fidelity [21]. The definition of Elmore delay is described by Eq.(2.6):

$$\vec{\tau_k} = G^{-1}C \tag{2.6}$$

For an RC tree structure with driver resistance  $R_d$  and total downstream capacitance  $C_i$  seen from tree node  $v_i$ , the Elmore delay from driver to a sink  $v_k$  can be recursively calculated as

$$\vec{\tau_k} = R_d C_0 + \sum_{e_{ij} \in path(v_0, v_k)} R_{ij} \left( \frac{C_{ij}}{2} + C_j \right)$$

(2.7)

Elmore delay tends to overestimate the interconnect delay because it does not correctly take the resistive shielding effect [22] into consideration. The degree of fidelity becomes lower as interconnect wires become thinner and longer. Hence we use Elmore delay model during the initial construction of the zero-skew clock structures and use an accurate higher-order delay metric to post-optimize the performance of of

Figure 2.4: A Circuit N and its adjoint circuit  $\eta$ .

the network. In our work, the higher-order delays are analytically obtained from the higher-order step response waveforms simulated by our HPRIMA-based simulator [9].

## 2.4 Transient Adjoint Sensitivity Analysis

Incremental sensitivity is defined as the partial derivative of a circuit response of interest with respect to a parameter of interest. It is valid in a small range around the nominal value of the parameter of interest. Direct sensitivity and adjoint sensitivity are two methods of the incremental sensitivity analysis, where the direct method solves the sensitivity of many circuit responses with respect to a single parameter while the adjoint methods calculates the sensitivity of one performance function with respect to many circuit parameter values [16, 23, 24]. In this thesis, the use of the adjoint method is a natural choice since we are interested in the sensitivity of the noise metric in power grids and the sensitivity of skew and transition time in clock networks with respect to all parameters in the interconnect circuit.

Adjoint sensitivity analysis is based on Tellegen's theorem (Eq. (2.8)), which states that the instantaneous power in any circuit is zero.

$$\sum v_b i_b = 0 \tag{2.8}$$

Given a pair of circuits with identical topologies (Figure 2.4), from Tellegen's theorem

and the KCL and KVL relations of each circuit, the following basic sensitivity relation over a time period of interest from  $t_0$  to  $t_f$  can be derived:

$$\sum_{all\ branches} \int_{t_0}^{t_f} [\varphi \delta v - \psi \delta i] dt = 0$$

(2.9)

A detailed derivation process can be found in [16] and will be skipped here. We summarize the analysis process as follows: applying Eq. (2.9) to circuit elements such as capacitors, inductors and resistors, choosing corresponding adjoint elements of the same value as those in the original circuit, defining a time axis variable  $\tau$  (for the purpose of analyzing the adjoint network) to be backward time t of the original network (i.e.,  $\tau = t_0 + t_f - t$ ), and setting initial conditions in the adjoint circuit zero and removing original voltage and current sources, we have the transient adjoint sensitivity formula as follows:

$$\int_{t_0}^{t_f} \frac{\partial f(t)}{\partial C} dt = -\int_{t_0}^{t_f} [\psi_C(\tau)\dot{v}_C(t)] dt$$

(2.10)

$$\int_{t_0}^{t_f} \frac{\partial f(t)}{\partial R} dt = \int_{t_0}^{t_f} [\varphi_R(\tau) i_R(t)] dt$$

(2.11)

$$\int_{t_0}^{t_f} \frac{\partial f(t)}{\partial L} dt = -\int_{t_0}^{t_f} [\varphi_L(\tau) \dot{i}_L(t)] dt$$

(2.12)

where f(t) is the performance function of interest.

The same notations will be used throughout the thesis, i.e. the voltages [currents] in the original network are denoted by v [i], while the voltages [currents] in the adjoint network are  $\psi$  [ $\varphi$ ], and the symbols t and  $\tau$  denote the temporal variables in the original and adjoint network, respectively.

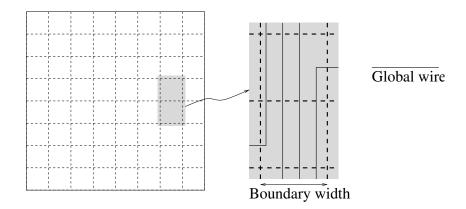

Figure 2.5: Wire congestion estimation based on tessellation on a chip.

## 2.5 Global Wire Congestion Measurement

In global routing, the entire chip is tessellated into an array of grid cells (shown in Figure 2.5) and the wiring information across the boundaries between neighboring grid cells is used to estimate the signal wire congestion distributions. If the capacity of a boundary b is C(b) and there are S(b) signal wires that cross the boundary, then the overflow on the boundary b is S(b) - C(b). All tile boundaries with negative overflow values form a congestion map for a chip. The wire density at b is represented as S(b)/C(b), measuring the congestion of b.

# Chapter 3

# Fast Analysis and Optimization of Structured Power/Ground Networks

#### 3.1 Introduction

The design of power/ground (P/G) networks is critical to the correct functioning of a chip. With the rapid increases in the clock frequency and reduction of feature sizes of high-speed electronic circuits, it is becoming more and more important to design and optimize P/G networks fast and efficiently. The major reasons that affect the circuit functionality are the voltage droop due to current flow in the network, ground bounce due to inductive effects, and possible electromigration effects due to excessive current densities. The first two can lead to unacceptable circuit switching speeds and/or glitches, while the latter places a limit on the useful lifetime of a chip [14].

#### 3.1.1 Previous Work

Various algorithms and simplified device models for P/G networks that offer faster but less accurate results have been explored in the past. Early work on P/G networks focuses on tree-like structures so as to allow the use of path tracing algorithms for efficiency [25, 26] and assumes resistance-only models for the network.

A 3-stage IR-drop analysis methodology during the whole design process is presented in [27]. The authors of [17] propose a hierarchical analysis technique and a novel sparsification method based on 0-1 integer linear programming. A PDE-like multigrid method is proposed in [18] to perform both DC and transient simulation of power grids efficiently. Each of the above methods aims at speeding up the analysis and predicting the power grid performance properly.

Other related work on optimizing P/G networks includes [28–30], which use techniques ranging from simulated annealing to the solution of a sequence of linear programs for wire widening, or [31], which optimizes the topology of the P/G network. A frequency domain sensitivity-based decoupling capacitor optimization method is proposed in [32]. [33] formulates the P/G network optimization problem as a nonlinear convex optimization problem.

#### 3.1.2 Motivation for Hybrid Topology

Most of the existing techniques have focused on methods that optimize a specific topology that is typically specified by the user to be a large and complex mesh. There is an inherent conflict between P/G networks that are easy to analyze, and those that provide reliable power levels and evenly distributed current densities. While tree structures provide all of the former benefits, they result in poor quality in P/G signal delivery. On the other hand, dense meshes are excellent in satisfying the latter requirement but are very computationally difficult to analyze. For example,

spice. The key idea used in this work is that an approach that meets both of these requirements would be something between a pure tree and a full mesh. In this work, we use one such topology skeleton with a global mesh feeding local trees, as described later in this section; a similar method has been used in [34]. However, we emphasize that this approach can be modified to other topologies that are intermediate to the two extremes of full trees and full meshes: one such example is a global mesh that feeds smaller unconnected local meshes.

We point out that such an approach may not be optimal for a high-performance full-custom microprocessor, where a dense mesh may be essential for reliable P/G levels<sup>1</sup>. However, we believe that it will be of great utility in ASIC design, where fast turnaround time of the design is a major criterion, and ease of analysis of the P/G network with an acceptable performance hit can greatly ease the task of P/G network optimization. For this scenario, we present an analysis/sensitivity calculation/optimization procedure in this chapter.

#### 3.1.3 Contributions

#### 3.1.3.1 Hybrid Mesh/Tree Structure

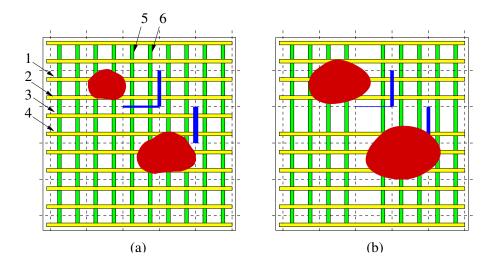

The P/G network model proposed here, characterized by the mesh/tree topology of [34], is illustrated in Figure 3.1; for simplicity, only one tree is shown in the figure. An overlying coarse mesh structure of a user-specified topology provides global distribution of the P/G signals across the chip. From various nodes of this mesh, tree structures of user-specified topologies originate and distribute the supply voltage to the utilization points, each of which is modeled as an equivalent RC branch. The

<sup>&</sup>lt;sup>1</sup>Even for processor designs, the use of more general hierarchical structures is not uncommon [17].

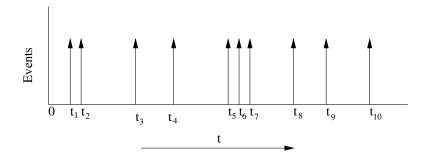

advantage of using an RC branch instead of an equivalent current source is that such a model also captures the loading effects of the utilization points on the P/G network. Practically, the designer often specifies a set of worst-case switching patterns and a list of the potential critical nodes in the network. Each specified switching event in a switching pattern provides information on which RC elements at the utilization points load the network at a given time. An example of a switching pattern for a given utilization point is shown in Figure 3.2, where each arrow indicates which RC element has entered or left the network due to a switching event at a gate.

Figure 3.1: A structured P/G bus topology.

Figure 3.2: Switching events at a node in a P/G network.

#### 3.1.3.2 Fast Noise and Sensitivity Analysis and Optimization

Figure 3.3: Voltage droop of node j in a power network during event i-1 and i.

As described in Chapter 2, the noise metric of a node between event i-1 and i is the integral of voltage droop beyond the noise margin, which is represented by the shaded area in Figure 3.3. The most critical node in the power/ground network is defined as the node with the maximum sum of voltage droop integrals over all switching events. Our optimization problem is to minimize the total P/G bus area, subject to the constraints that the voltage droop integral of the most critical node is less than or equal to zero. The process of optimizing the P/G network requires an iterative loop within which it is necessary to analyze the network to determine whether it satisfies specifications or not, and to determine gradient information to guide the optimization.

Several techniques may be used for this optimization: varying the topology, varying wire widths, and adding decoupling capacitors. In this work, we focus on optimization by varying wire widths and extend this technique to add decoupling capacitors.

The structure in Figure 3.1 is amenable to fast analysis, while also maintaining the performance by using mesh structures that reduce the voltage drops and current densities in the highest current regions. In [34], an AWE-based technique is proposed for simulating P/G networks. While AWE tends to be unstable at higher orders of approximation, for such a structure, the task of analysis is rapidly performed using PRIMA [5], a reduced order modeling technique that produces provably passive macromodels.

Transient sensitivity has been particularly useful in circuit optimization and tuning and has been used to provide gradient information, for example, in [35] and [19]. In the case of P/G network optimization, the optimization of the objective function requires the computation of transient sensitivity for the specified critical nodes with respect to all the elements in the whole circuit, and we employ the adjoint method [16].

Traditionally, transient sensitivity computation for a circuit with a fixed topology is performed by a convolution between the forward-in-time voltage/current slope of the element (capacitor, resistor or inductor) in the original circuit and the backward-in-time voltage/current across the same element in the adjoint circuit, where the same fixed topology is chosen for the pair of circuits.

In our work, the topology of the original P/G network changes at the beginning of each switching event as new RC elements are added to the network or removed from it. This chapter presents an appropriate extension of the adjoint network technique over multiple-intervals so that the sensitivities can be efficiently computed. Our sensitivity computation is coupled with an efficient PRIMA-based order reduction approach so that it can handle large-scale P/G circuits. A closed-form transient sensitivity expression is provided for a PRIMA approximation of a given order. Finally, a TILOS [6]-like heuristic optimization procedure is proposed.

# 3.2 Hierarchical Analysis of the P/G Network Incorporating Non-zero Initial Conditions

The procedure for analysis of the power and ground network is symmetric. In other words, it is enough to develop a solution technique for one of these, and it is easy to extend this to solve the other.

As described in Chapter 2, the interconnect in the P/G network is modeled as a large-scale RLC linear circuit. The simulation is event-driven, proceeding one interval at a time, starting from the first interval until the last, updating the corresponding switch states specified in the event list while moving from one interval to the next. The final state, i.e., capacitor voltages and inductor currents, at the end of each interval constitutes the initial state for the next interval. We assume that the initial conditions at all nodes in the network are at a user-specified level.

The entire system can be described by the Laplace equation

$$(G+sC)V(s) = J(s) (3.1)$$

The size of vector V(s) is equal to the sum of total number of mesh nodes, number of nonzero mesh and package inductances, total number of trees and each entire tree stamps. The objective of fast analysis is to reduce this system to a smaller system that captures the response of the system to the given set of inputs and the initial conditions in the system.

The hierarchical model reduction and simulation proceeds in three stages: first, all trees are reduced to an equivalent passive model. Next, the mesh is solved, along with these passive models to find all mesh voltages. Finally, these mesh voltages provide the voltage source at the root of each tree and are used to solve each tree individually and independently. This hierarchical approach serves to reduce the amount of computation required during the analysis.

#### 3.2.1 Reduction of the Trees

The MNA equation for each of the trees with initial conditions can be written as

$$(G_T + sC_T)V_T(s) = [J_1(s) \ J_2(s) \ J_3(s)]$$

(3.2)

where  $J_1(s)$  is the input excitation to the tree, which is 1 since we are interested in the transfer function (impulse response) of the tree during the later waveform propagation step. An initial condition at time T on a capacitor  $C_i[\text{inductor }L_i]$  may be modeled as a voltage [current] source of value  $V_{Ci}(T)$  [ $I_{Li}(T)$ ] in series [parallel] with a capacitor [inductor] with zero initial conditions. The vector  $J_2(s)$  captures these initial conditions of the tree and has entries of the type  $C_iV_{Ci}(T)$  and  $L_iI_{Li}(T)$ , where the multiplications by  $C_i$  and  $L_i$  correspond to conversions between Thevenin and Norton forms for ease of application for the formulation. The vector  $J_3(s)$  is only considered when an impulse current source or a current source of square wave is applied to the most critical node in the adjoint network discussed in Section 3.3.

The PRIMA reduction procedure is applied to obtain a provably passive tree reduction. A RICE-like tree traversal [36] computes the orthonormal basis X of the Krylov space, so that the procedure is extremely fast. The three-column right hand side matrix in Eq. (3.2) tells us that three columns are added to X in each iteration and to obtain a reduction of order  $q_T$ ,  $\lceil \frac{q_T}{3} \rceil$  iterations are required. While for the analysis of the original network, the right hand side only includes two columns ( $[J_1(s) \ J_2(s)]$ ) and consequently the number of iterations is  $\lceil \frac{q_T}{2} \rceil$ .

#### 3.2.2 Solving the Mesh

Substituting the reduced order model of each tree can reduce the MNA equation (3.1) for the whole system to

$$(G_m + sC_m)V_m(s) = J_m(s)$$

(3.3)

Comparing to the size of vector V(s), the size of vector  $V_m(s)$  is reduced to the sum of total number of mesh nodes, number of nonzero mesh and package inductances, total number of trees and each reduced tree stamps, which is still large. PRIMA is applied to Eq. (3.3) again to this reduced system to further reduce the system to a smaller order

$$(\tilde{G}_m + s\tilde{C}_m)\tilde{V}_m = \tilde{J}_m(s) \tag{3.4}$$

Since  $G_m$  is sparse, sparse matrix technique can be used to compute the orthonormal basis X of the Krylov space, where the inverse of the matrix  $\tilde{G}_m$  is required. Since the overlying mesh is typically small in terms of the number of nodes and the order of the final system  $q_m$  is small, the computational cost of this is also reasonably small.

The transient response of each mesh node in the P/G net is found to be:

$$V_{Mesh}(s) = \sum_{i=1}^{q_m} \frac{r_i}{s - \lambda_i} \tag{3.5}$$

where  $\lambda_i$  and  $r_i$  are the *i*th pole and residue of a mesh node.  $q_m$  is the number of dominant poles for the mesh, which is determined by the reduced order of the mesh matrix. After taking an inverse Laplace transform, we have

$$V_{Mesh}(t) = \sum_{i=1}^{q_m} r_i e^{\lambda_i t}, \quad 0 \le t \le T_f, \tag{3.6}$$

where  $T_f$  is the period of time between two continuous events.

#### 3.2.3 Propagating Waveforms Down the Trees

The solution to Eq. (3.4) is used to set the mesh node voltages to the computed value. These values are used to recursively compute the voltage at each of the internal node in the local trees. This process is continued until all the voltages and currents in the trees have been computed. The voltage at each node is computed as the sum of the zero input response and the zero initial condition response; note that the input for the tree is the voltage at the mesh node (root of the tree), which is typically nonzero.

The propagation formula of a tree node in Laplace domain is

$$V_{Tree}(s) = \sum_{j=1}^{q_T} \frac{r_{Tz_j}}{s - \lambda_{Tz_j}} + \sum_{i=1}^{q_m} \sum_{j=1}^{q_T} \frac{r_i}{s - \lambda_i} \times \frac{r_{Timp_j}}{s - \lambda_{Timp_j}},$$

(3.7)

where  $\lambda_{Tz_j}$  and  $r_{Tz_j}$  are the jth pole and residue of the local tree's zero input response,  $\lambda_{Timp_j}$  and  $r_{Timp_j}$  are the jth pole and residue of its impulse response.  $q_T$  is the number of dominant poles for each local tree. Eq. (3.7) can further be derived into the following form using the partial fractional method:

$$V_{Tree}(s) = \sum_{i=1}^{Q_T} \frac{r_{T_i}}{s - \lambda_{T_i}}$$

$$(3.8)$$

where  $Q_T = q_m + q_T$  and the poles of the tree are

$$\lambda_T = \begin{cases} \lambda_i, & i = 1 \cdots q_m \\ \lambda_{Timp_j} = \lambda_{Tz_j}, & j = 1 \cdots q_T \end{cases}$$

(3.9)

and the corresponding residues are

$$r_T = \begin{cases} \sum_{j=1}^{q_T} \frac{r_i r_{1imp_j}}{\lambda_i - \lambda_{Timp_j}}, & i = 1 \cdots q_m \\ r_{Tz_j} + \sum_{i=1}^{q_m} \frac{r_{Timp_j} r_i}{\lambda_i - \lambda_{Timp_j}}, & j = 1 \cdots q_T \end{cases}$$

(3.10)

By taking inverse Laplace Transform we get:

$$V_{Tree}(t) = \sum_{i=1}^{Q_T} r_{T_k} e^{\lambda_{T_k} t}, \ 0 \le t \le T_f$$

(3.11)

Currents flowing through mesh branches are solved from the MNA equation of the mesh, while every tree branch current flowing through node i and j is found through  $i(s) = (v_i(s) - v_j(s))/(R_{ij} + sL_{ij})$  and by taking an inverse Laplace transform of i(s) we can get i(t).

# 3.3 Adjoint Sensitivity Computation Over Multiple Intervals

Adjoint sensitivity analysis is a standard technique for circuit optimization where the sensitivity of one output with respect to many parameter values is required [16]. In adjoint sensitivity analysis, Tellegen's theorem is applied to a pair of circuits with the same topology by combining the branch currents and voltages at any two instants of time.

For our problem, we simulate the P/G network over the specified event list. At the beginning of each event, a set of switching activities occurs, with some RC elements switching out of the network and others switching in. This complicates the task of adjoint sensitivity computation since the topology changes for each interval. One contribution of this work is to extend adjoint analysis to this variable topology.

The basis for adjoint analysis comes from Tellegen's theorem, which when integrated over a time period of interest from  $t_0$  to  $t_f$ , gives

$$\sum_{all\ branches} \int_{t_0}^{t_f} \left[ \varphi(\tau) \delta v(t) - \psi(\tau) \delta i(t) \right] dt = 0$$

(3.12)

Suppose there are a total of f + 1 events, each event is lasting from  $t_{k-1}$  to  $t_k$ , k=1 to f, where  $t_0=0$ . Then (13) becomes

$$\sum_{\substack{\text{all branches}\\ \text{pranches}}} \sum_{k=1}^{f-1} \int_{t_{k-1}}^{t_k} [\varphi^{(k)}(\tau)\delta v^{(k)}(t) - \psi^{(k)}(\tau)\delta i^{(k)}(t)]dt = 0$$

(3.13)

The superscript  $^{(k)}$  denotes the voltage or current response corresponding to the topology between switching event k-1 and k.

If we are interested in the sensitivity of v(t) at some moment t, we isolate  $\delta v(t)$  by setting all voltage sources in the adjoint circuit to zero. The left-hand side of the sensitivity term becomes

$$\sum_{all \ current \ sources} \left[ \sum_{k=1}^{f-1} \int_{t_{k-1}}^{t_k} -\varphi^{(k)}(\tau) \delta v^{(k)}(t) dt \right]$$

(3.14)

Suppose the most critical voltage droop occurs at  $t = T_{peak}$ . To obtain the term  $\delta v(T_{peak})$ , we set an impulse current source at the node of interest in the adjoint network, i.e.,

$$\varphi^{(p)}(\tau) = -\delta(t - T_{peak}) \tag{3.15}$$

where  $t_{p-1} < T_{peak} < t_p$ . Only for interval  $t_{p-1} < T_{peak} < t_p$ , this term is non-zero:

$$\int_{t_{p-1}}^{t_p} \delta(t - T_{peak}) \delta v^{(p)}(t) dt = \delta v^{(p)}(T_{peak})$$

(3.16)

which is exactly what is desired in the left-hand side of the sensitivity term.

As described in Section 3.1, in our work, the performance of power/ground network is measured using the shaded area beyond the threshold voltage (noise margin) shown in Figure 3.3. Suppose the most critical node has only one overshoot between  $t_{sk}$  and  $t_{ek}$  during event k, the sum of shaded area over all switching events can be represented as

$$Z = \sum_{k=1}^{f} \int_{t_{sk}}^{t_{ek}} [NM_H - v(t)] dt$$

(3.17)

As discussed in [19], instead of applying an impulse current source of  $-\delta(t - T_{peak})$ , a current pulse of  $u(t - t_{sk}) - u(t - t_{ek})$ , k = 1...f, is applied to the most critical node. Then Eq. (3.14) becomes:

$$\sum_{k=1}^{f} \int_{t_{k-1}}^{t_k} \left[ -u(t - t_{sk}) + u(t - t_{ek}) \right] \delta v(t) dt = \sum_{k=1}^{f} \int_{t_{sk}}^{t_{ek}} -\delta v(t) dt = \delta Z$$

(3.18)

which, similar to Eq. (3.16), is exactly what is desired in the left-hand side of the sensitivity term.

#### 3.3.1 Sensitivity with Respect to Capacitors

For capacitors, we have the device equation

$$i_C = C\dot{v}_C(t)$$

$$\delta i_C(t) = C\delta\dot{v}_C(t) + \dot{v}_C(t)\delta C$$

(3.19)

From Eq. (3.13), the right-hand side of the sensitivity term becomes

$$\sum_{k=1}^{f} \int_{t_{k-1}}^{t_k} \left\{ \varphi_C^{(k)}(\tau) \delta v_C^{(k)}(t) - \psi_C^{(k)}(\tau) [C \delta \dot{v}_C^{(k)}(t) + \dot{v}_C^{(k)}(t) \delta C] \right\} dt \tag{3.20}$$

We can integrate by part the  $\delta \dot{v}_{C}^{(k)}(t)$  term in Eq. (3.20) to obtain<sup>2</sup>:

$$\sum_{k=1}^{f} \left[ -\psi_{C}^{(k)}(\tau) C \delta v_{C}^{(k)}(t) \right]_{t_{k-1}}^{t_{k}} - \delta C \int_{t_{k-1}}^{t_{k}} \psi_{C}^{(k)}(\tau) \dot{v}_{C}^{(k)}(t) dt \\

+ \sum_{k=1}^{f} \int_{t_{k-1}}^{t_{k}} \left[ \varphi_{C}^{(k)}(\tau) \delta v_{C}^{(k)}(t) + C \dot{\psi}_{C}^{(k)}(\tau) \delta v_{C}^{(k)}(t) \right] dt$$

(3.21)

As in normal adjoint calculation, to avoid negative energy storage elements, we choose  $\tau$  to be the backward time in each interval k. Thus we have

$$\tau = t_{k-1} + t_k - t \tag{3.22}$$

The capacitor in the adjoint circuit can be chosen as

$$\varphi_C(\tau) = -C\dot{\psi}_C(\tau) = -C\frac{d\psi(\tau)}{dt} = C\frac{d\psi(\tau)}{d\tau}$$

(3.23)

which is an ordinary capacitor. So Eq. (3.21) becomes

To remove the integration-by-parts term in Eq. (3.24), we use the following procedure:

-

$$\psi_C^f(t_{f-1}) = 0$$

(initial conditions for the adjoint circuit is set to zero)

<sup>-</sup>  $\psi_C^f(t_{f-1}) = 0$  (initial conditions for the adjoint circuit is set to zero)

2 Note that  $\dot{\psi}_C$  and  $\dot{v}_C$  are not defined everywhere. In particular, at switching time points, the derivatives can be discontinuous although the function is continuous. However, removing a finite number of points constitutes the removal of a set of zero measure and does not alter the evaluated value of the integral, where  $\dot{\psi}_C$  and  $\dot{v}_C$  are continuous [37].

- $\psi_C^k(t_k) = \psi_C^{k-1}(t_{k-2}), k = 2, \dots, f$

- $\delta v_C^1(t_0) = 0$  (by definition, since the initial conditions of the original circuit are known)

This will set all the non-integral terms in Eq. (3.24) to zero. In case there is only one interval, this result reduces to the conventional adjoint sensitivity calculation procedure [16] that sets  $\psi_C(t_0) = 0$ . It can be inferred from this that the adjoint circuit simulation proceeds in the backward order of event (time).

The transient sensitivity formula with respect to capacitor C at the moment of  $T_{peak}$  is as follows:

$$\frac{\delta v^{(p)}(T_{peak})}{\delta C} = -\sum_{k=1}^{p} \int_{t_{k-1}}^{t_k} \psi_C^{(k)}(t_{k-1} + t_k - t) \dot{v}_C^{(k)}(t) dt$$

(3.25)

where  $t_{p-1} < T_{peak} < t_p$ . Notice that since zero-initial conditions are set in the adjoint circuit and there is no excitation until  $t = T_{peak}$  (assuming  $t_0 = 0$ ), i.e., until  $\tau = t_f - T_{peak}$ ,  $\psi_C(\tau) = 0$  when  $\tau < t_f - T_{peak}$ .  $\psi_C(\tau)$  is continuous over the period  $t_f \ge \tau \ge t_f - T_{peak}$ . In other words,  $\psi_C(t)$  is continuous over the period  $0 \le t \le T_{peak}$ .

Similarly, the sensitivity of Z with respect to capacitor C is:

$$\frac{\delta Z}{\delta C} = -\sum_{k=1}^{f} \int_{t_{k-1}}^{t_k} \psi_C^{(k)}(t_{k-1} + t_k - t) \dot{v}_C^{(k)}(t) dt$$

(3.26)

where  $\psi_C(\tau)$  is the voltage droop across capacitor C under the current excitation of  $u(\tau - \tau_{sk}) - u(\tau - \tau_{ek})$ ,  $\tau_{sk} = t_{k-1} + t_k - t_{ek}$  and  $\tau_{ek} = t_{k-1} + t_k - t_{sk}$ , applied to the most critical node.

#### 3.3.2 Sensitivity with Respect to Resistors and Inductors

The sensitivity with respect to resistors and inductors can be derived similarly:

- Apply a current source of  $-\delta(t T_{peak})$  (referring to Eq. (3.16)) or  $u(t t_{sk}) u(t t_{ek})$  (referring to Eq. (3.18)) at the most critical node.

- Set  $\tau = t_{k-1} + t_k t$  for each interval k to maintain  $d\tau/dt = -1$ .

- Choose  $\psi_R(\tau) = R\varphi_R(\tau)$  and  $\psi_L(\tau) = L\dot{\varphi}_L(\tau)$ .

- Set initial conditions in the adjoint circuit to zero.

- Simulate the circuit in the backward order of event

Specifically, for RLC circuits, the transient sensitivity formula with respect to R and L at  $T_{peak}$  are

$$\frac{\delta v^{(p)}(T_{peak})}{\delta R} = \sum_{k=1}^{p} \int_{t_{k-1}}^{t_k} \varphi_R^{(k)}(t_{k-1} + t_k - t) i_R^{(k)}(t) dt

\frac{\delta v^{(p)}(T_{peak})}{\delta L} = -\sum_{k=1}^{p} \int_{t_{k-1}}^{t_k} \varphi_L^{(k)}(t_{k-1} + t_k - t) \dot{i}_L^{(k)}(t) dt$$

(3.27)

where  $t_{p-1} < T_{peak} < t_p$ . Similarly,  $\varphi_R(t)$  and  $\varphi_L(t)$  are continuous over the period  $0 \le t \le T_{peak}$ .

Similarly, the sensitivity of Z with respect to R and L are

$$\frac{\delta Z}{\delta R} = \sum_{k=1}^{f} \int_{t_{k-1}}^{t_k} \varphi_R^{(k)}(t_{k-1} + t_k - t) i_R^{(k)}(t) dt

\frac{\delta Z}{\delta L} = -\sum_{k=1}^{f} \int_{t_{k-1}}^{t_k} \varphi_L^{(k)}(t_{k-1} + t_k - t) \dot{i}_L^{(k)}(t) dt$$

(3.28)

#### 3.3.3 Closed-form Transient Sensitivity Formula

The simulation technique as discussed in Section 3.2 can be applied to analyze the adjoint P/G network in backward time. The only trouble happens with the current source of  $u(\tau - \tau_{sk}) - u(\tau - \tau_{ek})$  is applied to the most critical node for every event k. The Laplace transform of such a current source will make the right-hand side matrix of (3) or (4) a non-constant. Such a problem can be avoided by computing

the response to the current source of  $\delta(\tau)$  applied to the most critical node instead. If such a response is  $\omega(s)$ , then the response to  $u(\tau - \tau_{sk}) - u(\tau - \tau_{ek})$  is  $v(s) = \omega(s)(e^{-s\tau_{sk}} - e^{-s\tau_{ek}})/s$ .

The event-driven simulation of the adjoint P/G network is performed in a backward order of the specified events, so that the topology of the adjoint network is also changing in the reverse temporal order. The response of the tree with the most critical node is the superposition of  $v(\tau) = L^{-1}(v(s))$ , the voltage response propagated from the root (mesh node) and its zero-input response which is nonzero for all the backward the model and its zero-input response which is nonzero for all the backward the model are the magnificant and branch current i(t) (for resistors or inductors) having the following form as indicated from Eq. (3.6) and (3.11):

$$f^{k}(t) = \sum_{i=1}^{P} r_{i} e^{\lambda_{i} t}, \quad 0 \le t \le T_{k}, \quad T_{k} = t_{k} - t_{k-1}, \tag{3.29}$$

the nodal voltage  $\psi(\tau)$  (for capacitors) and branch current  $\varphi(\tau)$  (for resistors or inductors) can be represented as

$$g^k(\tau) =$$

$$\begin{cases}

\sum_{j=1}^{Q} r_{z_{j}} e^{\Lambda_{j}\tau}, & 0 \leq \tau \leq T_{k} - t_{e_{k}} \\

\sum_{j=1}^{Q} r_{z_{j}} e^{\Lambda_{j}\tau} + \sum_{j=1}^{Q+1} R_{j} e^{\Lambda_{j}(\tau - T_{k} + t_{e_{k}})}, & T_{k} - t_{e_{k}} \leq \tau \leq T_{k} - t_{s_{k}} \\

\sum_{j=1}^{Q} r_{z_{j}} e^{\Lambda_{j}\tau} + \sum_{j=1}^{Q+1} R_{j} e^{\Lambda_{j}(\tau - T_{k} + t_{e_{k}})} - \sum_{j=1}^{Q+1} R_{j} e^{\Lambda_{j}(\tau - T_{k} + t_{s_{k}})}, & T_{k} - t_{s_{k}} \leq \tau \leq T_{k},

\end{cases}$$

(3.30)

where  $T_k = t_k - t_{k-1}$ ,  $\Lambda_j$  is the *j*th pole,  $r_{zj}$  is the *j*th residue of the zero-input response and  $R_j$  is the *j*th residue of the response to the current source of  $u(\tau - \tau_{sk})$  -  $u(\tau - \tau_{ek})$  at every switching event k.

Transient adjoint sensitivity calculation is performed using formula (27) or (29). As an example, the transient adjoint sensitivity of Z with respect to a capacitor C

can be computed as:

$$\frac{\partial Z}{\partial C} = \sum_{k=1}^{f} \left\{ -\int_{0}^{T_{k}} \sum_{i=1}^{P} r_{i} \lambda_{i} e^{\lambda_{i}t} \sum_{j=1}^{Q} r_{z_{j}} e^{\Lambda_{j}(T_{k}-t)} dt \right.$$

$$-\int_{0}^{t_{e_{k}}} \sum_{i=1}^{P} r_{i} \lambda_{i} e^{\lambda_{i}t} \sum_{j=1}^{Q+1} R_{j} e^{\Lambda_{j}(t_{e_{k}}-t)} dt + \int_{0}^{t_{s_{k}}} \sum_{i=1}^{P} r_{i} \lambda_{i} e^{\lambda_{i}t} \sum_{j=1}^{Q+1} R_{j} e^{\Lambda_{j}(t_{s_{k}}-t)} dt \right\}$$

$$= \begin{cases}

-\sum_{i=1}^{P} \sum_{j=1}^{Q} r_{i} \lambda_{i} r_{z_{j}} e^{\Lambda_{j}T_{k}} T_{k} \\

-\sum_{i=1}^{P} \sum_{j=1}^{Q+1} r_{i} \lambda_{i} R_{j} e^{\Lambda_{j}t_{e_{k}}} t_{e_{k}} + \sum_{i=1}^{P} \sum_{j=1}^{Q+1} r_{i} \lambda_{i} R_{j} e^{\Lambda_{j}t_{s_{k}}} t_{s_{k}}, \quad \lambda_{i} = \Lambda_{j}$$

$$-\sum_{i=1}^{P} \sum_{j=1}^{Q} \frac{r_{i} \lambda_{i} r_{z_{j}} [e^{\lambda_{i}T_{k}} - e^{\Lambda_{j}T_{k}}]}{\lambda_{i} - \Lambda_{j}} \\

-\sum_{i=1}^{P} \sum_{j=1}^{Q+1} \frac{r_{i} \lambda_{i} R_{j} [e^{\lambda_{i}t_{e_{k}}} - e^{\Lambda_{j}t_{e_{k}}}]}{\lambda_{i} - \Lambda_{j}} + \sum_{i=1}^{P} \sum_{j=1}^{Q+1} \frac{r_{i} \lambda_{i} R_{j} [e^{\lambda_{i}t_{s_{k}}} - e^{\Lambda_{j}t_{s_{k}}}]}{\lambda_{i} - \Lambda_{j}}, \quad \lambda_{i} \neq \Lambda_{j}$$

$$(3.31)$$

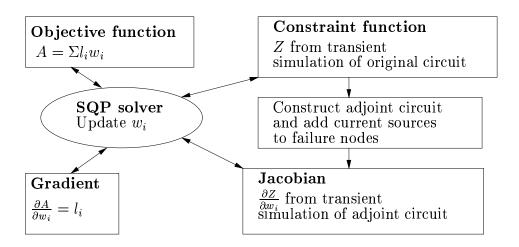

#### 3.4 Heuristic Optimization

The optimization technique used in this work is a sensitivity-based heuristic that is similar to the TILOS [6] algorithm, which is a greedy heuristic optimizer that changes the parameters that provide the "biggest bang for the buck." The basic philosophy of optimizing the P/G network using this technique is to try to reduce the maximum voltage droop violation in the network with the minimum increase in the area, by successively increasing parameter sizes by a small amount in each iteration.

The problem of optimizing a P/G network by varying wire widths can be formulated as

$$Minimize \ Area = \sum_{i} l_i w_i$$

$Subject \ to \ Max(Z) \le 0$

In the objective function,  $l_i$  represents the total length of a set of the P/G wire segments with width  $w_i$ . In each iteration, we first analyze the network to identify

the most critical node with the maximum voltage droop integral, then determine the parameter of the network that this critical node is most sensitive to, and finally bump up the width of this parameter by a certain small amount so that the most critical voltage droop integral is reduced.

In our method, we divide each wire in the mesh/trees into several  $\pi$ -segments, but model a set of adjacent wires as having the same width in order to reduce the network of optimization parameters. The gradients with respect to the area  $A_i$  of each set of N wires with width  $w_i$  is computed using the chain rule as follows:

$$\frac{\partial Z}{\partial A_i} = \frac{\partial Z}{\partial w_i} \times \frac{\partial w_i}{\partial A_i} = \frac{\partial Z}{\partial w_i} \times \frac{1}{\sum\limits_{j=1}^{N} l_j}$$

(3.32)

and

$$\frac{\partial Z}{\partial w_i} = \sum_{j=1}^{N} \left[ \frac{\partial Z}{\partial C_{j1}} \frac{\partial C_{j1}}{\partial w_j} + \frac{\partial Z}{\partial C_{j2}} \frac{\partial C_{j2}}{\partial w_j} + \frac{\partial Z}{\partial R_j} \frac{\partial R_j}{\partial w_j} + \frac{\partial Z}{\partial L_j} \frac{\partial L_j}{\partial w_j} \right]$$

(3.33)

where the set of wires with width  $w_i$  consists of N wire segments; each of the segment j has resistance  $R_j$ , inductance  $L_j$ , and capacitance  $C_{j1}$ ,  $C_{j2}$  at each terminal of the wire.

From Eq. (2.1), it is easy to see that

$$\frac{\partial R_j}{\partial w_i} = -\rho l_j / w_j^2 \tag{3.34}$$

$$\frac{\partial L_j}{\partial w_j} = -\gamma l_j / w_j^2 \tag{3.35}$$

$$\frac{\partial C_{j1}}{\partial w_j} = \frac{\partial C_{j2}}{\partial w_j} = \frac{\beta l_j}{2} \tag{3.36}$$

The overall optimization procedure is as follows:

- Simulate the original P/G network over the entire period using the hierarchical simulation method discussed in Section 3.2.

- Determine the most critical node with its  $Z_{max}$ .

- Save voltage approximants (poles and residues) for all C's and current approximants for all R's and L's in the network.

- Simulate the adjoint network backward in time (event) with zero initial conditions.

- Save voltage/current waveforms for the adjoint network.

- Compute the voltage sensitivities with respect to all R's, L's and C's.

- Compute the voltage sensitivities with respect to  $A_i$  using Eq. (3.32), (3.33), (3.34), (3.35) and (3.36).

- Bump up the width of the set of wires with maximum sensitivity by multiplying it with a small factor (< 1.1).

- Repeat the above procedure until the maximum voltage droop integral in the network is below zero.

The above procedure can be extended to include the optimization of decoupling capacitors. The objective of this optimization is to determine appropriate sizes of each wire and each decoupling capacitor for the minimum area overhead. Initially, decoupling capacitors with some small values are connected to some user-specified nodes in the P/G network. The gradients of the most critical node with respect to these decoupling capacitors are exactly the transient adjoint sensitivities calculated in each iteration. The cost function for the optimization is a weighted sum of the wire area and the areas of all the decoupling capacitors. In each iteration, either the wire width or the decoupling capacitor with the maximum sensitivity with respect to the objective function will be increased with a small factor until the constraints are met.

#### 3.5 Experimental Results

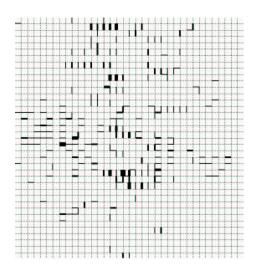

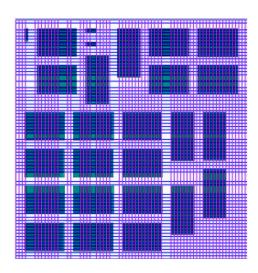

The simulation and optimization procedure was implemented in C, and the results on several P/G networks were tested. The networks were constructed randomly for power delivery to a 2cm x 2cm chip in a  $0.18\mu m$  technology with  $V_{dd}=1.65V$ . The set of events is randomly generated and is different for each circuit. The results shown here can be considered to correspond to a top level P/G distribution network, since complete P/G networks may have several millions of nodes. The utilization points here would correspond to functional blocks, each of which is reduced to an equivalent RC representation.

We have used the commercial simulator, HSPICE, to analyze the speed and accuracy of our simulation results. All experiments are performed on Sun Ultra-60 Workstations.

The waveforms for two networks are shown in Figure 3.4, with the waveforms using HSPICE plotted concurrently on the same figures using dotted lines. In each case, our waveform and that of HSPICE are quite close. The order of approximation is chosen such as the integral of noisy area is within 10% to that of HSPICE.