This is to certify that I have examined this copy of a doctoral dissertation by

Jaskirat Singh Bindra

and have found that it is complete and satisfactory in all aspects,

and that any and all revisions required by the final

examining commitee have been made.

Professor Sachin S. Sapatnekar

Name of the Faculty Adviser

Signature of the Faculty Adviser

Date

GRADUATE SCHOOL

# VARIATION-AWARE COMPUTER-AIDED DESIGN TECHNIQUES FOR VLSI DIGITAL CIRCUITS

A DISSERTATION SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA

BY

JASKIRAT SINGH BINDRA

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

Sachin S. Sapatnekar, Adviser

October 2006

© Jaskirat Singh Bindra 2006

#### ACKNOWLEDGEMENTS

The most important contributor for the successful completion of this thesis without any doubt is, my adviser, Prof. Sachin Sapatnekar. It is fair to say that without Sachin's suggestions, patience, and work ethics, I would have had a much more extended stay as a graduate student. My modest success as a researcher owes a lot to his indefatigable efforts to mentor me in my work and to teach me how to be meticulous in technical writing and presentation. In additional to being an excellent adviser, Sachin is a also a great person, which is bit of a rarity, as many of my graduate student friends, from other groups, would enviously admit.

I would like to express my gratitude to Prof. Paul Johnson's research, (from the Carlson School of Management, University of Minnesota) and to Semiconductor Research Corporation for providing financial support for my graduate education.

Thanks are also due to the former and current members of the *VEDA* lab and Prof. Kia Bazargan's lab, Shrirang Karandikar, Rupesh Shellar, Haifeng Qian, Anup Sultania, Brent Goplen, Tianpei Zhang, Yong Zhan, Vidyasagar Nookala, Sanjay Kumar, Cristinel Ababei and Pongstorn Maidee. I have had several useful discussions with them on technical and other topics. Special thanks to Hongliang Chang for providing the code of the *MinSSTA* software package and help with the benchmark circuits.

My five years in the Twin Cities were made most enjoyable by the wonderful group of friends I found here. Without the time spent with Aditya Saxena, Abhinav Das, Sourabh Dighe, Karthikeyan Bhasyam, Ranjit Eswaran, Manish Kapoor (Usman Khan), Nikhil Wale, Sagar Nookala, Salim Charaniya, Deepa Deepa and Anil Singh Bika, life would have been very uninspiring. These people were the ones who made Minnesota a home away from home for me.

The support of my big extended family has helped me overcome some of the difficult times I have had. Finally, the person I am and the life that i enjoy, is all due to the hard work and sacrifices of my parents. I am fortunate to have parents who have given me complete independence to explore my interests and the courage to pursue my dreams. Without their struggles and efforts, my ability to even start this thesis would not have existed. Dedicated to the wonderful family that i was lucky enough to have been born in.

#### ABSTRACT

One of the most significant challenges currently confronting the VLSI circuit design community is the problem of ever increasing variations in the manufacturing process and the operating environment of high performance digital circuits. The escalating impact of environmental and process variations on the performance of current and future technology VLSI circuits, necessitates the use of circuit design techniques that can account for these uncertainties.

From a circuit design perspective, the variations may be classified as controllable or uncontrollable in nature. Controllable variations are a class of variations that can be directly reduced or controlled by circuit design techniques that specifically target these types of variation. Some examples of such variations are temperature fluctuations, which can be controlled by modifying the temporal and spatial distribution of hot spots on chip, and voltage variation, which can be controlled by optimizing the power grid of a chip. The variations that are uncontrollable in nature are those for which a circuit design cannot exercise any direct influence. From the point of view of a circuit designer, most variations arising from the limitations of the manufacturing process are uncontrollable in nature. Although uncontrollable variations cannot be directly reduced, their impact on the circuit performance can be controlled by robust circuit design techniques. To enable such robust circuit design, it becomes essential for VLSI computer-aided design (CAD) tools to keep sufficient design margins by incorporating their effect. This thesis presents variation-aware design automation techniques, accounting for both controllable and uncontrollable types of variations, by focusing on three important issues in digital circuit design: power grid design, gate sizing, and timing analysis.

The first part of the thesis addresses the problem of mitigating the controllable variations in the operating environment of a digital circuit, manifested in the form of voltage drop on the power supply network of wires. To control the voltage variations, two topology optimization heuristics for the design of power ground networks have been proposed. These power grid design techniques maintain the desirable property of regular structure of the supply network by proposing a locally regular, globally irregular power grid topology. The first power grid design scheme is based on a sensitivity based heuristic, which iteratively adds wire in the local regions of the power grid to obtain maximum reduction in the voltage drop on the grid wires, for a given increase in the wire area. A second power distribution network design algorithm is presented, based on a recursive bipartitioning approach. This algorithm runs considerably faster than the first one by utilizing the idea of *locality* of power grid, and employing abstractions of different parts of the power grid circuit. Our proposed piecewise-uniform grid topology has a better wire area utilization as compared to other commonly used grid topologies, and our power grid design algorithm runs considerably faster compared to some previous approaches.

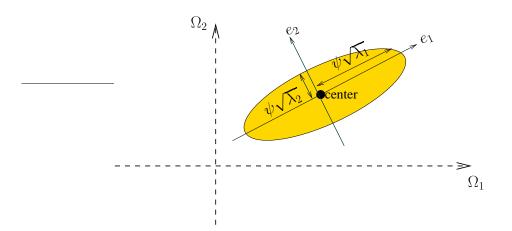

In the next part of the thesis, we focus on the problem of improving the timing yield of a digital circuit by performing gate sizing in the presence of uncontrollable manufacturing process variations. Our method formulates this robust gate sizing problem as a geometric program by employing posynomial delay models and a bounded *uncertainty ellipsoid* variation model for the random process parameters. Through our formulation, we provide a novel worst-casing solution that reduces the pessimism involved in worst-casing by incorporating the effects of spatial correlations of circuit parameters in the optimization procedure. We use a graph pruning technique to reduce the number of constraints and intermediate variables for the optimization set up. This uncertaintyaware gate sizing problem is then solved efficiently using convex optimization tools. Experimental results show that for the same circuit area, our robust gate sizing solution has a better timing yield than the conventional, deterministically based worst-case gate sizing solution.

The last part of the thesis explores the problem of performing circuit timing analysis in the face of randomly varying process parameters. A statistical static timing analysis (SSTA) technique, which incorporates correlated parameters, both Gaussian and non-Gaussian, is developed to predict the probability distribution of the circuit delay. Prior to our work, most SSTA techniques could handle only a few correlated non-Gaussian variables. The proposed technique is the first scalable SSTA method, which can include correlated non-Gaussian parameters of variation in the statistical timing analysis framework. The SSTA procedure employs *independent component analysis (ICA)* as a preprocessing step, which enables the procedure to efficiently handle the correlated non-Gaussian parameters. Our algorithm has a linear complexity ( $O(n * N_G)$ ) in the number of grids (n), and the number of gates ( $N_G$ ) in the circuit. We demonstrate the accuracy of our SSTA procedure by verifying it with the Monte Carlo analysis.

#### TABLE OF CONTENTS

| 1 | Intr | oductio | 'n                                                        | 1  |

|---|------|---------|-----------------------------------------------------------|----|

|   | 1.1  | Variati | ions: Trends and Sources                                  | 2  |

|   | 1.2  | Resear  | rch Problems and Contributions                            | 6  |

|   | 1.3  | Organ   | ization of the Thesis                                     | 11 |

| 2 | Pow  | er Grid | l Design Algorithms                                       | 12 |

|   | 2.1  | Introd  | uction to Power Grid Design                               | 12 |

|   | 2.2  | Previo  | ous Work                                                  | 14 |

|   | 2.3  | Propos  | sed Power Grid Topology                                   | 16 |

|   | 2.4  | Prelim  | ninaries                                                  | 19 |

|   |      | 2.4.1   | Power Grid Circuit Model                                  | 19 |

|   |      | 2.4.2   | Terminology                                               | 21 |

|   | 2.5  | Circui  | t Analysis by Macromodeling                               | 22 |

|   | 2.6  | Soluti  | on Technique 1: A Sensitivity-based Heuristic             | 25 |

|   |      | 2.6.1   | Building the Power Grid                                   | 27 |

|   |      | 2.6.2   | Port Approximation Technique                              | 29 |

|   |      | 2.6.3   | Voltage Sensitivity Calculation                           | 31 |

|   |      | 2.6.4   | Congestion-Aware Power Grid Design                        | 40 |

|   |      | 2.6.5   | Optimization Objective and Constraints                    | 43 |

|   |      | 2.6.6   | Speedup Techniques                                        | 45 |

|   |      | 2.6.7   | Extension to Multiple Metal Layers                        | 45 |

|   |      | 2.6.8   | Experimental Results                                      | 46 |

|   | 2.7  | Soluti  | on Technique 2: A Partition-based Approach using Locality | 53 |

|   |      | 2.7.1   | Locality in the Structure of Power Grid                   | 55 |

|   |      | 2.7.2   | Outline of the Power Grid Design Procedure                | 57 |

|   |      | 2.7.3   | Grid Refinement                                           | 59 |

|   |       | 2.7.4     | Power Grid Design by Recursive Bipartitioning               | 61 |

|---|-------|-----------|-------------------------------------------------------------|----|

|   |       | 2.7.5     | Post Processing for Wire Alignment                          | 72 |

|   |       | 2.7.6     | The Complete Algorithm                                      | 73 |

|   |       | 2.7.7     | Extension to Multiple Layers                                | 77 |

|   |       | 2.7.8     | Experimental Results                                        | 79 |

|   | 2.8   | Conclu    | usion                                                       | 88 |

| 3 | Rob   | ust Gat   | e Sizing Techniques                                         | 90 |

|   | 3.1   | Introdu   | uction to Robust Gate Sizing                                | 91 |

|   | 3.2   |           | Ũ                                                           | 93 |

|   | 3.3   |           |                                                             | 96 |

|   |       | 3.3.1     | Geometric Programming                                       | 96 |

|   |       | 3.3.2     | Deterministic Gate Sizing as a Geometric Program            | 97 |

|   |       | 3.3.3     | The Ellipsoidal Uncertainty Set                             | 99 |

|   |       | 3.3.4     | Chi-square Distribution                                     | 00 |

|   | 3.4   | Variati   | on-Aware Gate Sizing 1                                      | 01 |

|   |       | 3.4.1     | Effect of Variations on Constraints                         | 01 |

|   |       | 3.4.2     | Robust GP formulation                                       | 04 |

|   |       | 3.4.3     | Overestimation of Variations                                | 08 |

|   |       | 3.4.4     | Graph Pruning                                               | 10 |

|   |       | 3.4.5     | Using Variable Size Ellipsoids                              | 17 |

|   |       | 3.4.6     | Incorporating Spatial Correlations                          | 20 |

|   |       | 3.4.7     | The Complete Sizing Procedure                               | 23 |

|   | 3.5   | Experi    | mental Results                                              | 24 |

|   | 3.6   | Conclu    | usion                                                       | 31 |

| 4 | Stati | istical T | iming Analysis Incorporating Correlated Non-Gaussian Param- |    |

# eters

| 5 | Sum  | mary                                                                | 173 |

|---|------|---------------------------------------------------------------------|-----|

|   | 4.13 | Conclusion                                                          | 171 |

|   |      | 4.12.2 SSTA results for Case 2                                      | 168 |

|   |      | 4.12.1 SSTA results for Case 1                                      | 166 |

|   | 4.12 | Experimental Results                                                | 165 |

|   | 4.11 | Time Complexity Analysis                                            | 163 |

|   |      | 4.10.2 The "max" Operation                                          | 160 |

|   |      | 4.10.1 The "sum" Operation                                          | 159 |

|   | 4.10 | SSTA Procedure                                                      | 159 |

|   | 4.9  | Moment-Matching-based PDF Extraction                                | 156 |

|   | 4.8  | Preprocessing to Evaluate the Moments of the Independent Components | 154 |

|   |      | 4.7.2 Generating Samples of Correlated Non-Gaussian Variables       | 150 |

|   |      | 4.7.1 The Cocktail Party Problem                                    | 148 |

|   | 4.7  | Independent Component Analysis                                      | 147 |

|   | 4.6  | Delay Representation                                                | 146 |

|   | 4.5  | Non-Gaussianity in SSTA                                             | 142 |

|   | 4.4  | Generating Moments from Process Data                                | 139 |

|   | 4.3  | Outline of the SSTA Procedure                                       | 137 |

|   | 4.2  | Previous Work                                                       | 134 |

|   | 4.1  | Introduction to SSTA                                                | 132 |

| 5 Summa | ry |

|---------|----|

|---------|----|

#### LIST OF TABLES

| 1.1  | Trends in IC technology parameters [SIA05]                                | 1  |

|------|---------------------------------------------------------------------------|----|

| 1.2  | Trends in parameters variations [Nas00]                                   | 3  |

| 2.1  | Errors for port approximations for a $10 \times 10$ grid                  | 31 |

| 2.2  | Errors for port approximations for a $12 \times 12$ grid                  | 32 |

| 2.3  | A Table lookup example to illustrate the simplification of voltage sen-   |    |

|      | sitivity computation.                                                     | 36 |

| 2.4  | A comparison of the wire area used by the locally regular, globally       |    |

|      | irregular power grids, designed using the proposed method, and the        |    |

|      | grids employing a globally regular structure, and a constant wire size    | 48 |

| 2.5  | A comparison of the wire area used by the locally regular, globally       |    |

|      | irregular power grids, designed using the proposed method, and the        |    |

|      | grids employing a globally regular structure, with irregular wire sizing. | 50 |

| 2.6  | A comparison of non-congestion-aware and congestion-aware, piecewise-     |    |

|      | uniform power grid design.                                                | 51 |

| 2.7  | Various tradeoffs involving number of ports kept, number of wires added   |    |

|      | in each iteration, reduction in wire area, runtime, and accuracy in power |    |

|      | grid design                                                               | 52 |

| 2.8  | Results of power grids designed by the proposed scheme for both flip-     |    |

|      | chip and wire-bond cases.                                                 | 81 |

| 2.9  | A wire area and runtime comparison of the two proposed power grid         |    |

|      | design methods.                                                           | 83 |

| 2.10 | Results of power grids designed for flip-chip circuits by the proposed    |    |

|      | method and the multigrid-based scheme.                                    | 84 |

| 2.11 | Results of power grids designed for flip-chip circuits by the proposed    |    |

|      | method and the exact wire sizing scheme.                                  | 86 |

| 2.12 | Power grids designed for pg-6 floorplan by choosing different partition-               |

|------|----------------------------------------------------------------------------------------|

|      | ing levels                                                                             |

| 3.1  | A timing yield comparison of deterministic and robust gate sizing so-                  |

|      | lutions                                                                                |

| 3.2  | A comparison of the robust and worst case gate sizing designs using                    |

|      | the same area                                                                          |

| 3.3  | A comparison of robust gate sizing solutions, with and without using                   |

|      | graph pruning and variable size ellipsoids                                             |

| 3.4  | A comparison of the robust gate sizing designs obtained by changing                    |

|      | the pruning cost function of Equation (3.38)                                           |

| 4.1  | A cumulative frequency table for 500 randomly generated values of $L_e$                |

|      | with $\mu_{L_e} = 65 \ nm$ and $\sigma_{L_e} = 5.2 \ nm$                               |

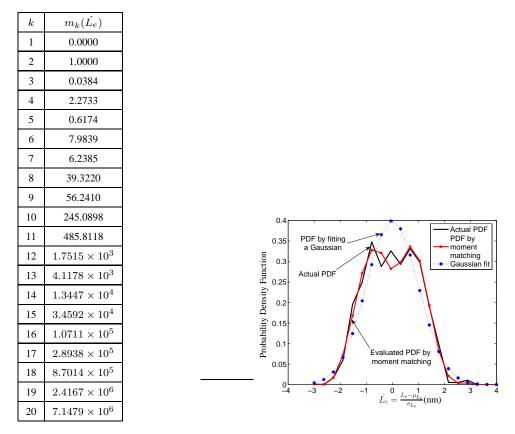

| 4.2  | A table showing the first twenty moments of $\hat{L}_e$ values listed in Table 4.1.140 |

| 4.3  | A comparison of results of the proposed SSTA method with Monte                         |

|      | Carlo simulation . $W$ parameters are modeled as non-Gaussian vari-                    |

|      | ables, and $L_e$ parameters are modeled as Gaussian variables                          |

| 4.4  | A comparison of results of the proposed SSTA method with Monte                         |

|      | Carlo simulation . $L_e$ parameters are modeled as non-Gaussian vari-                  |

|      | ables, and $W$ parameters are modeled as Gaussian variables 169                        |

| 4.5  | A runtime comparison the proposed SSTA with Gaussian SSTA and                          |

|      | Monte Carlo simulation                                                                 |

#### LIST OF FIGURES

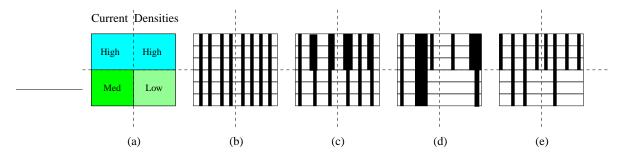

| 2.1 | (a) Current densities for an example chip that illustrates the possible     |    |

|-----|-----------------------------------------------------------------------------|----|

|     | choices for a power grid topology. Possible Designs of P/G Network          |    |

|     | (b) Grid with 4 wires in each tile and regular wire sizing. (c) Grid with   |    |

|     | 3 wires in each tile and irregular wire sizing. (d) A non-uniform grid      |    |

|     | with variable pitches throughout and irregular sizing. (e) A piecewise-     |    |

|     | uniform grid with 4 wires in the upper half tiles, 2 wires in bottom-left   |    |

|     | tile and 1 wire in bottom-right tile and uniform sizing                     | 18 |

| 2.2 | A power grid and its equivalent circuit model under DC conditions           | 20 |

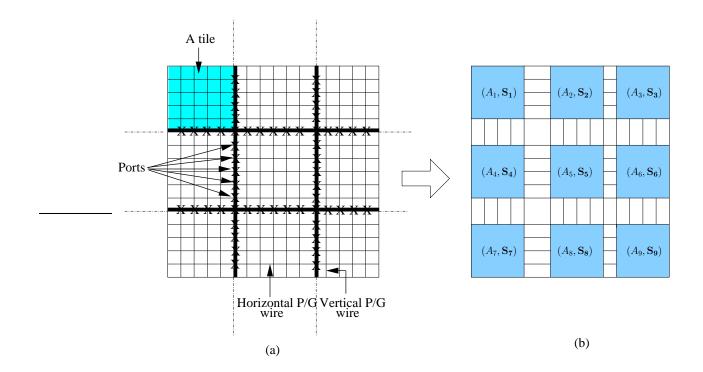

| 2.3 | Converting the P/G network to a system of macromodels. (a) A P/G            |    |

|     | network with port nodes at the tile boundaries. (b) The P/G network         |    |

|     | changed to a system of macromodels connected to each other through          |    |

|     | the port nodes.                                                             | 24 |

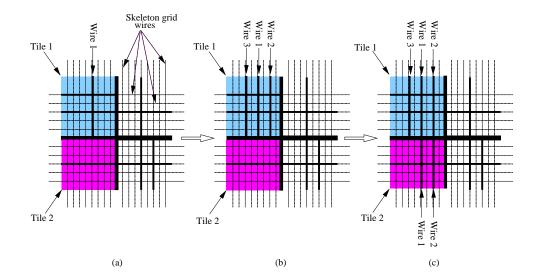

| 2.4 | Illustration of the procedure to build the power grid on a skeleton grid.   |    |

|     | The P/G wires must lie on the skeleton grid, shown with light lines. The    |    |

|     | positions of actual P/G wires are shown with dark lines. (a) The initial    |    |

|     | structure of the grid. (b) The structure of the grid after two wires are    |    |

|     | added in tile 1. The wires are added to maintain a near-constant pitch      |    |

|     | within the tile. (c) The grid structure after addition of two wires in tile |    |

|     | 2. The wires in tiles 1 and 2 are added at the same local positions so      |    |

|     | that they are aligned with each other.                                      | 27 |

| 2.5 | Reducing the number of ports of a tile of a power grid. (a) A tile of the   |    |

|     | original P/G network with 20 port nodes. (b) The port nodes of the tile     |    |

|     | reduced to 14 by combining some nodes.                                      | 30 |

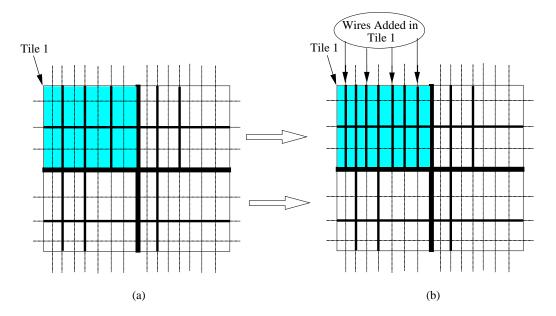

| 2.6  | Change in the grid structure by addition of wires in tile 1. (a) Tile 1          |    |

|------|----------------------------------------------------------------------------------|----|

|      | with 3 wires initially. (b) Four more wires added in tile 1. The corre-          |    |

|      | sponding change in macromodel parameters $(A_1, \mathbf{S_1})$ can be calculated |    |

|      | using Table 2.3 as a lookup table.                                               | 37 |

| 2.7  | (a) An example of a chip divided into four tiles demarcated with thick           |    |

|      | dark lines representing P/G wires. The P/G wires inside a tile are shown         |    |

|      | with thin dark lines. (b) A tile is further divided into 16 bins. The dark       |    |

|      | lines are P/G wires inside the tile.                                             | 41 |

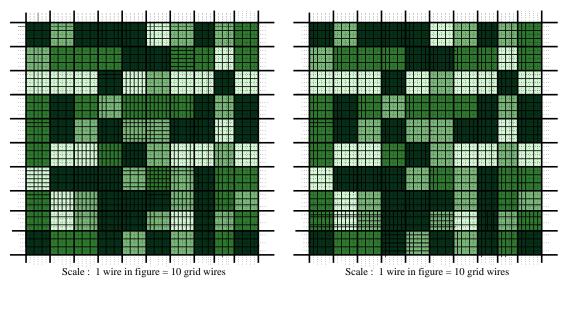

| 2.8  | The wire density pattern of power grids constructed by the proposed              |    |

|      | optimization for a 2cm×2cm chip divided into 100 tiles, superimposed             |    |

|      | over the current density patterns. The regions with darker shades have           |    |

|      | higher current densities.                                                        | 47 |

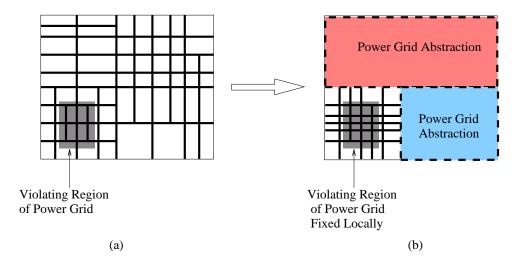

| 2.9  | The concept of locality in power grid design. (a) A detailed power grid          |    |

|      | with a violating region shown with the shaded rectangle. (b) Details of          |    |

|      | regions of power grid far from the violating region abstracted away and          |    |

|      | the violations fixed locally.                                                    | 56 |

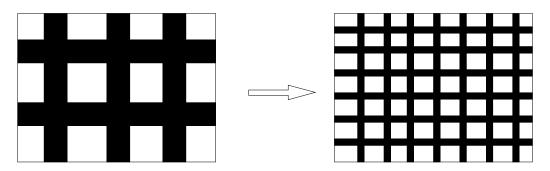

| 2.10 | A power grid with thick wires and large pitch refined to a grid with             |    |

|      | thinner wires and smaller pitch.                                                 | 60 |

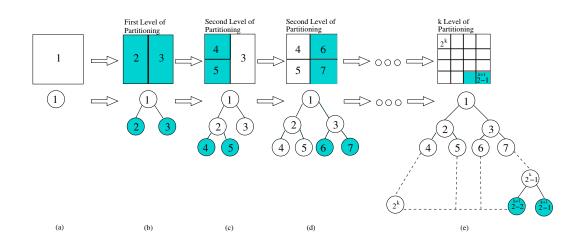

| 2.11 | The recursive bipartitioning process to design the power grid. Each              |    |

|      | partition cut is equivalent to adding two elements in the binary parti-          |    |

|      | tion_tree. The height of the tree represents the level of partitioning. The      |    |

|      | two shaded elements refer to the two partitions where the new power              |    |

|      | grid is designed in the current iteration.                                       | 61 |

| 2.12 | First level of partitioning: A chip divided into two partitions and the          |    |

|      | power grid constructed in the two partitions.                                    | 63 |

| 2.13 | Power grid constructed in the two partitions changed to a system of              |    |

|      | macromodels. The macromodels connect with each other through the                 |    |

|      | port nodes on the partition wire.                                                | 64 |

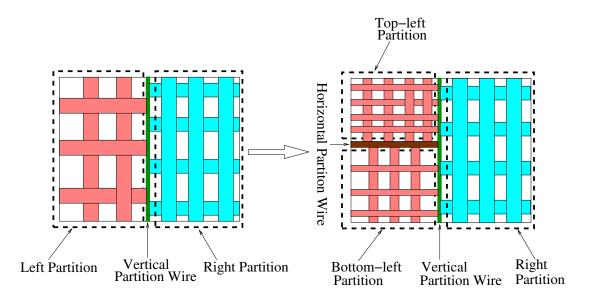

| 2.14 | The second partitioning level in the power grid design procedure. The       |    |

|------|-----------------------------------------------------------------------------|----|

|      | coarse grids in the left and the right partitions are refined in this level | 66 |

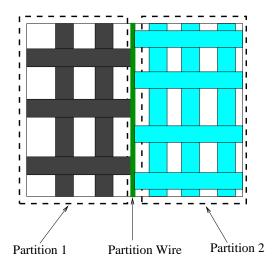

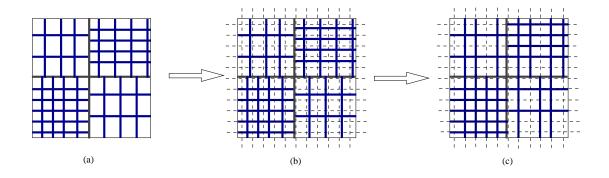

| 2.15 | The post-processing step to align the power grid wires in different par-    |    |

|      | titions. (a) Power grid wires in adjacent partitions are misaligned. (b)    |    |

|      | A minimum pitch virtual grid, shown with dashed lines is constructed        |    |

|      | over the entire layout area. (c) The power grid wires are moved to the      |    |

|      | nearest position on the virtual grid. The wires in adjacent partitions are  |    |

|      | better aligned now.                                                         | 72 |

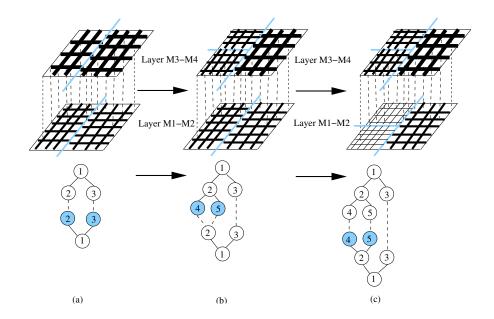

| 2.16 | Extending the grid design procedure to multiple metal layers M1to M4.       |    |

|      | The dashed lines between the top two and the bottom two layers repre-       |    |

|      | sent via connections between layers M2 and M3. (a) First level of par-      |    |

|      | titioning has been completed for the metal layers M3-M4. Grids in the       |    |

|      | left and right partitions for the bottom two layers are being designed.     |    |

|      | (b) The top-left and bottom-left partitions for layers M3-M4 being pro-     |    |

|      | cessed in the second level of partitioning for the top two metal layers.    |    |

|      | (c) The top-left and bottom-left partitions for layers M1-M2 being pro-     |    |

|      | cessed in the second level of partitioning for the bottom two metal layers. | 77 |

| 3.1  | An uncertainty ellipsoid set in two dimensions. The ellipsoid set is used   |    |

|      | as a bounded model for multivariate normal parameter variations 1           | 00 |

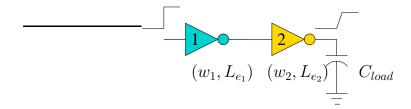

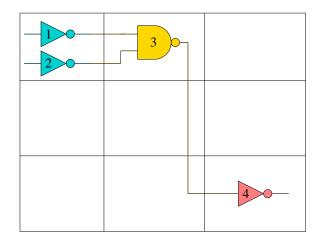

| 3.2  | A simple example circuit to explain the geometric program formulation       |    |

|      | for robust gate sizing problem                                              | 04 |

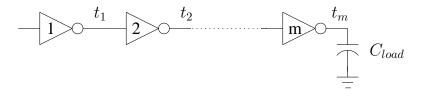

| 3.3  | An example of a chain of inverters circuit to explain the problem of        |    |

|      | overestimation of variations in the robust GP formulation 1                 | 08 |

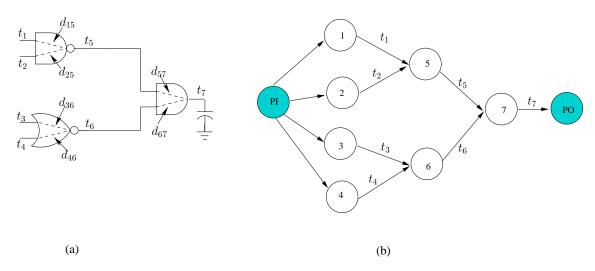

| 3.4  | A simple example circuit to illustrate the graph pruning method. (a) A      |    |

|      | two-level combinatorial circuit. (b) Timing graph for the circuit 1         | 11 |

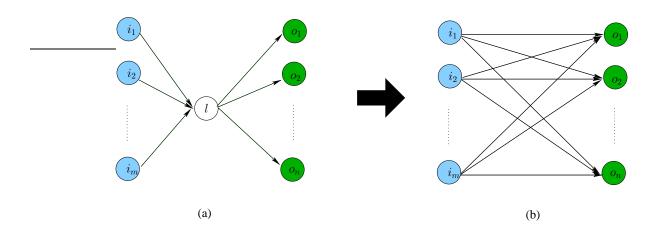

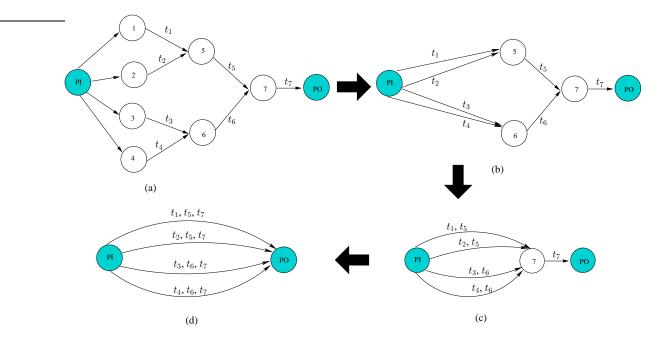

| 3.5 | A segment of the timing graph of a circuit to illustrate the removal of a          |     |

|-----|------------------------------------------------------------------------------------|-----|

|     | node in the graph pruning method. (a) The original graph segment. (b)              |     |

|     | The graph segment after pruning node $l. \ldots \ldots \ldots \ldots \ldots$       | 112 |

| 3.6 | The graph pruning method applied to the example circuit of Figure 3.4.             |     |

|     | (a) The original circuit graph. (b) Graph after removing nodes 1, 2, 3             |     |

|     | and 4. (c) Graph after removing nodes 5 and 6. (d) The final pruned                |     |

|     | graph                                                                              | 114 |

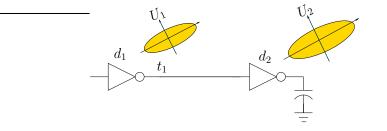

| 3.7 | An example circuit to explain the use of variable size ellipsoids to re-           |     |

|     | duce the pessimism in the robust GP formulation                                    | 118 |

| 3.8 | A grid based spatial correlation model. The layout is divided into a               |     |

|     | $3\times3$ grid. The gates in the same grid are assumed to have a perfect          |     |

|     | correlation. Gates in the nearby grids are assigned a high correlation             |     |

|     | factor, and the gates in far away grids are assigned a low or a zero               |     |

|     | correlation factor                                                                 | 121 |

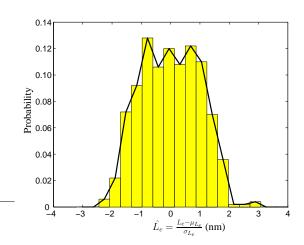

| 4.1 | A frequency histogram of the $\hat{L_e}$ values listed in Table 4.1                | 139 |

| 4.2 | PDF of $\hat{L}_e$ values listed in Table 4.1                                      | 140 |

| 4.3 | A simple circuit example to illustrate the effect of non-Gaussian pa-              |     |

|     | rameters on the PDF of the circuit delay.                                          | 142 |

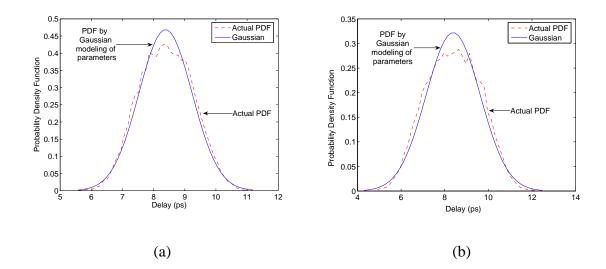

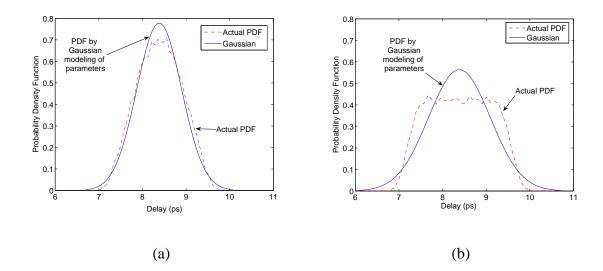

| 4.4 | PDF of the delay of the example circuit of Figure 4.3, when $\{W_1, W_2\}$         |     |

|     | are modeled as uniformly distributed, and $\{L_{e_1}, L_{e_2}\}$ are modeled as    |     |

|     | normally distributed random variables for (a) uncorrelated and (b) cor-            |     |

|     | related $W$ and $L_e$ process variables                                            | 144 |

| 4.5 | PDF of the delay of the example circuit of Figure 4.3, when $\{L_{e_1}, L_{e_2}\}$ |     |

|     | are modeled as uniformly distributed, and $\{W_1, W_2\}$ are modeled as            |     |

|     | normally distributed random variables for (a) uncorrelated and (b) cor-            |     |

|     | related $W$ and $L_e$ process variables                                            | 145 |

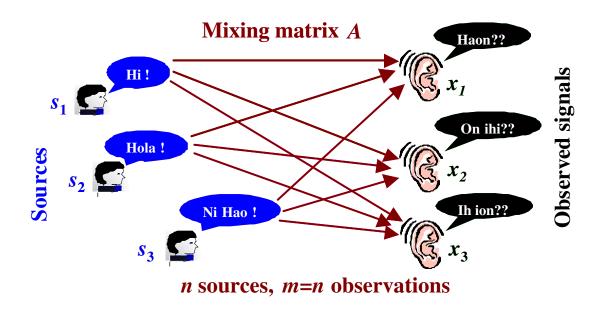

| 4.6 | The cocktail party problem to illustrate the independent component      |     |  |  |

|-----|-------------------------------------------------------------------------|-----|--|--|

|     | analysis set up                                                         | 148 |  |  |

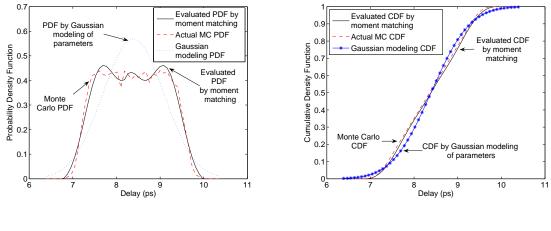

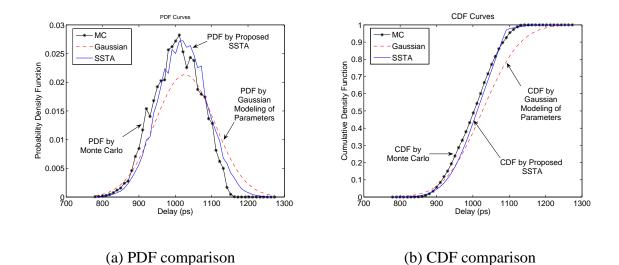

| 4.7 | Extracted PDF and CDF for the delay of the example circuit              | 157 |  |  |

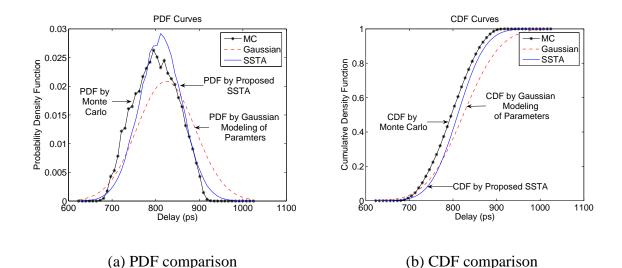

| 4.8 | A comparison of SSTA and Monte Carlo distribution for circuit s13207.   | 171 |  |  |

| 4.9 | A comparison of the results of SSTA and Monte Carlo for circuit s38417. | 172 |  |  |

"Much to learn you still have ... my old padawan. ... This is just the beginning!" -Master Yoda in Attack of the Clones

## Chapter 1 Introduction

The self-fulfilling prophecy of Gordon Moore's law [Moo65], predicting that the number of transistors on a chip would approximately double every eighteen months, has led to aggressive technology scaling and shrinking of the feature size. As a direct consequence of technology scaling, from only a few transistors in 1965 [Moo65], hundreds of millions of transistors are being integrated on a chip today. Table 1.1, compiled from the latest version of International Technology Roadmap for Semiconductors (ITRS) [SIA05], lists some of the trends in technology scaling, and indicates an estimate of more than three-quarters of a billion transistors on a single chip in 30nm technology in 2010.

| Year | Technology | Number of   | Number of   | f     | $V_{DD}$ | Power |

|------|------------|-------------|-------------|-------|----------|-------|

|      | Node (nm)  | Transistors | Wire Levels | (GHz) | (V)      | (W)   |

| 2005 | 54         | 193M        | 11          | 5.2   | 1.1      | 167   |

| 2006 | 48         | 193M        | 11          | 6.8   | 1.1      | 180   |

| 2007 | 42         | 386M        | 12          | 9.3   | 1.1      | 189   |

| 2008 | 38         | 386M        | 12          | 11.0  | 1.0      | 198   |

| 2009 | 34         | 386M        | 12          | 12.4  | 1.0      | 198   |

| 2010 | 30         | 773M        | 12          | 15.0  | 1.0      | 198   |

| 2011 | 27         | 773M        | 12          | 17.7  | 0.9      | 198   |

Table 1.1: Trends in IC technology parameters [SIA05].

This astronomical number of on-chip transistors chip, makes it increasingly difficult to control the operating conditions of the chip. The variations in the operating environment, such as the temperature and voltage changes lead to the problem of signal integrity and variable delay of a circuit. The limitations of the deep-submicron fabrication process technology and new physical phenomena that express themselves as small geometries, make it practically impossible to control the dimensions of the critical device parameters. The manufacturing process-driven uncertainties in the device parameters results in causing a spread in circuit performance measures such as the delay and power. While the signal integrity issues arising from the environmental variations may cause a chip to fail in the worst case, the variations in the circuit parameters affect the timing and power yield of the chip.

The increasing impact of environmental and process variations on the performance of current and future technology VLSI circuits necessitates the use of circuit design techniques that can account for these uncertainties. Given the complexities of these variations, it is essential for the VLSI computer-aided design (CAD) tools to incorporate their effect, in order to enable the design of robust circuits that are insensitive to the variations as much as possible. This thesis focuses on such VLSI CAD techniques for variation-aware design of digital circuits. We address the problems arising from environmental and process-driven variations and provide robust design automation solutions to these problems.

In this chapter, we will first discuss some trends in and sources of environmental and process variations, and then list the contributions of our research and explain the organization of this thesis.

## 1.1 Variations: Trends and Sources

Although variations have been a long standing problem, trends in current and future technologies have made their impact a much more serious problem than it has ever been.

Table 1.2, compiled from [Nas00], shows the trends in the mean ( $\mu$ ), and the standard deviation ( $\sigma$ ), of some important circuit parameters namely, the effective channel length ( $L_e$ ), gate oxide thickness ( $T_{ox}$ ), on-chip supply voltage ( $V_{DD}$ ), n-mos transistor

| Parameters           | 1997  |           | 1999  |           | 2002  |           | 2005  |           | 2006  |           |

|----------------------|-------|-----------|-------|-----------|-------|-----------|-------|-----------|-------|-----------|

|                      | $\mu$ | $3\sigma$ |

| $L_e$ (nm)           | 250   | 80        | 180   | 60        | 130   | 45        | 100   | 40        | 70    | 33        |

| $T_{ox}$ (nm)        | 5     | 0.4       | 4.5   | 0.36      | 4     | 0.39      | 3.5   | 0.42      | 3     | 0.48      |

| $V_{DD}$ (V)         | 2.5   | 0.25      | 1.8   | 0.18      | 1.5   | 0.15      | 1.2   | 0.12      | 0.9   | 0.09      |

| $V_{th}$ (V)         | 0.5   | 0.05      | 0.45  | 0.045     | 0.4   | 0.04      | 0.35  | 0.04      | 0.3   | 0.04      |

| $W_{int}$ ( $\mu$ m) | 0.8   | 0.2       | 0.65  | 0.17      | 0.5   | 0.14      | 0.4   | 0.12      | 0.3   | 0.1       |

| $T_{int}$ ( $\mu$ m) | 1.2   | 0.3       | 1     | 0.3       | 0.9   | 0.27      | 0.8   | 0.27      | 0.7   | 0.25      |

| $ ho(\Omega m)$      | 45    | 10        | 50    | 12        | 55    | 19        | 60    | 19        | 75    | 25        |

threshold voltage ( $V_{th}$ ), interconnect width ( $W_{int}$ ), thickness ( $T_{int}$ ) and resistivity ( $\rho$ ).

Table 1.2: Trends in parameters variations [Nas00].

It is clear from this data, that the  $\sigma/\mu$  ratio increases significantly as technology scales from 250 nm to 70 nm. Moreover, the number of parameter variations affecting the performance of the circuit is rapidly increasing. Some examples of the sources of these environmental and process variations are listed below.

1. *Supply Voltage Variations:* Shrinking of device sizes results in exponential increase in the chip densities. These extremely large number of devices draw large amounts of currents from the power/ground (P/G) distribution network of wires, which connect to all the transistors on the chip. Together with the increase in the amounts of current drawn, the resistances of the interconnects have also increased due to the decrease in wire widths. Moreover, the amount of currents drawn from the power grid wires in a given region of the chip varies, depending on the switching activities of the gates in the underlying functional block. For instance, an arithmetic-logic unit (ALU) block is likely to exhibit a much higher switching activity, on an average, than a cache unit. This variable switching behavior of the functional blocks results in different current density regions of the

chip, which leads to the problem of a variable voltage drop in the supply wires and fluctuations in the supply voltage distributed to the on-chip transistors.

2. Subwavelength Lithography: In nanometer technologies, the minimum feature sizes are much smaller than the wavelength of light used in the photolithography process. For example, 193 nm lasers are currently used to fabricate the devices of dimensions 90nm or less [GKSY03, SIA05]. Thus, the ability to precisely control the critical dimensions of devices in the nanometer regime becomes increasingly difficult.

In the current technology nodes, not only the critical dimensions of the minimum feature size line, but also the quality of line and line edges is gaining importance. The line edge roughness of photoresist lines and the corresponding polysilicon lines is becoming significant as gate linewidth control becomes comparable to the size of the photoresist polymer unit. The current state-of-the-art roughness for sub-100nm gate length technology has been reported to be of the order of 5-15 nm [KWW04], which may lead to significant device parameter fluctuations.

- 3. *Diffusion Process for Nanometer Devices:* As the devices become smaller, the number of dopant atoms per transistors fall in the range of 10 to 100 [BKD04]. At these levels, it becomes extremely difficult for the diffusion and the ion implantation process technology to exactly guarantee a uniform number of dopant atoms for every transistor. This random dopant density causes variations in the threshold voltage of transistors on chip [AK98].

- 4. *Chemical-Mechanical Planarization:* Variations in interconnect height and width can arise from the chemical-mechanical planarization (CMP) process, and results from the difference in hardness between the interconnect material and the dielectric. Ideally, after etches have been trenched into the dielectric below an interconnect layer and copper on the wafer, the CMP process should remove the unwanted

copper, leaving only the wires and vias. However, as the copper line is softer than the dielectric material, erosion due to CMP process causes uneven removal of copper and dielectric, resulting in variations in the interconnect dimensions.

The above list is not exhaustive as several other sources of variations affect the circuit performance.

From a design perspective, these variations may be broadly classified into two categories:

- Controllable Variations: These are a class of variations that can be controlled directly by a circuit designed specifically to target these types of variation. Some examples of such variations are temperature and voltage fluctuations. A designer can use some well-known circuit design techniques to reduce the voltage and temperature variations. For instance, a method to appropriately place thermal vias in the chip area is likely to help in controlling the temperature gradient across the chip. Similarly, a scheme to ably size the wires of the power supply network or place decoupling capacitors (decaps) at the appropriate locations could aid in reducing the voltage variations.

- Uncontrollable Variations: The variations that are uncontrollable in nature are those for which a circuit design cannot cause any direct reduction. From the perspective of a designer, the process-driven uncertainties in the channel length, transistor width, via resistance, oxide thickness, etc., are uncontrollable in nature. However, the desired circuit performance must be achieved in spite of these uncontrollable variations. Although it is not possible to directly control or reduce these types of variations, it is still possible to account for their impact on the circuit performance. A circuit designer usually relies on some type of guard-banding approach to control the effect of these uncontrollable variations. To achieve the desired circuit performance, in the presence of these types of uncertainties, extra resources such as larger transistors, wider wires, redundant logic are typically

used.

### **1.2 Research Problems and Contributions**

In this thesis, we propose CAD solutions for problems related to both controllable and uncontrollable type of variations. Specifically, we propose solutions to the following problems:

- 1. Power distribution network design: The P/G network of wires electrically connect the external  $V_{DD}$  and ground nodes to all the on-chip transistors. The problem of voltage drop <sup>1</sup> on these P/G wires, is a case of variations in the operating environment of a chip. These variations can be regarded as controllable variations, as circuit design techniques can directly control or reduce them. We present two topology optimization techniques for the design a high performance power supply network, subject to various reliability constraints.

- In the first power grid design technique, we propose a sensitivity based greedy heuristic, which analytically estimates the reduction in voltage drop with an increase in the wire area, in different regions of the chip area, and then iteratively selects the most sensitive region for wire additions. We extend this approach to include a congestion cost in our objective function so that the construction of grids by our method does not aggravate the congestion problem. Compared to other commonly used grid structures, the power grids designed by our procedure show considerable savings in the wire area. However, the runtimes achieved by our algorithm are not very fast.

- To overcome the efficiency issues in our first power grid design scheme, we present a second algorithm based on the idea of hierarchical grid design and the notion of locality (to be explained in Section 2.7) in power grid design.

<sup>&</sup>lt;sup>1</sup>Also referred to as the IR drop problem.

This grid design procedure employs a recursive bipartitioning approach and uses abstractions of parts of the power grid system.

Our methods propose and optimize for a novel piecewise-uniform power grid topology, that is suggested in our work. Such a topology, employing a locally regular, globally irregular grid structure, has the advantages of judicious use of wire area, combined with the relative ease of grid design. Experimental results show that our algorithm is considerably fast: we can design large power grids consisting of thousands of wires, and more than a million nodes in about 6 to 13 minutes of runtime. Our proposed designs achieve significant savings in wire area compared to other grid topologies (about 12% to 24% reduction), and the power grids designed by a multigrid-based previous work [WMS05] (about 6% to 12% reduction). The abovementioned power grid design schemes were published in [SS05] and [SS06b].

2. Robust gate sizing: The variations arising from the process limitations result in the circuit parameters such as the transistor channel length, width, oxide thickness and dopant density to deviate from their nominal values. This results in change of the circuit delay from the original nominal value that it was designed for. If the deviation of the delay from its nominal value is a positive shift, the new delay could exceed the original target delay, and cause a decrease in the timing yield of the chip, which is defined as the fraction of total number of manufactured chips that meet the original delay specifications. Thus, the presence of random variations in the circuit parameters could lead to reducing the profitability of the manufactured chips. From a gate sizing point of view, the presence of these random perturbations can be seen as uncontrollable type of variations. These uncertainties, arising from the fabrication process limitations, cannot be directly controlled or reduced by a gate sizing scheme. However, their effect on the circuit performance can be controlled. By accounting for the worst-case impact of these variations on the

circuit timing, the desired timing yield can still be achieved.

Traditionally, the robust gate sizing problem has been solved by guard-banding approaches. These methods are based on padding the timing constraints by a margin that safeguards against the effect of variations. However, most of these methods employ an arbitrary amount of guard-banding, e.g., by setting the original delay specification much tighter than the required target delay. Such ad hoc methods fail to capture important statistical attributes of the circuit such as the path correlations or the spatial correlations between varying parameters, and may result in overly pessimistic designs, spending more resources than necessary to achieve a specified timing yield.

In this thesis, we propose a novel and an efficient worst-casing methodology for the robust gate sizing problem. Our scheme reduces the pessimism involved in traditional worst-casing methods by incorporating the effect of spatial correlations in the optimization procedure. We employ a bounded model for the parameter variations, in the form of an uncertainty ellipsoid, which captures the spatial correlation information between the physical parameters such as channel lengths and transistor widths. The use of the uncertainty ellipsoid, along with the assumption that the random variables, corresponding to the varying parameters, follow a multivariate Gaussian distribution, enable us to size the circuits for a specified timing yield. The value of the desired timing yield can be chosen from the quantile function tables of the well-known *Chi-square* distribution [JW02]. In our formulation, we reduce the problem of overestimation of the variational components of the delay terms, by employing a circuit graph pruning technique [VC99], and using variable size ellipsoids at different topological levels of the circuit. Generating a first order Taylor series approximation of posynomial gate delay models, we formulate the resulting robust optimization problem as a geometric program [BV04]. The optimization problem is solved using highly efficient convex optimization methods

such as the interior point algorithm. Experimental results show that for the same transistor area, the circuits sized by of our robust optimization approach have, on an average, 12% fewer timing violations as compared to the gate sizing solutions obtained via the traditional, deterministically based guard-banding method. An early version of this work was published in [SNLS05].

3. Statistical timing analysis incorporating correlated non-Gaussian parameters: The presence of random variations in the physical parameters of the transistors, and the interconnects of a circuit make the results of deterministic static timing analysis (STA) mostly irrelevant. To provide meaningful information that the designers can use for the desired optimization tradeoffs in the presence of parameter uncertainties, the timing analysis methods must be variation-aware. Traditional variation-aware timing analysis techniques consist of performing a multicorned-based analysis or a Monte Carlo analysis. Both these methods suffer from some serious weaknesses. The corner-based analysis involves enumerating all possible corners, i.e., all combinations of min/max values of each varying parameter, which can be exponential in the number of parameters. More importantly, a corner-based methodology can arrive at a worst-case corner which may actually have an extremely low probability of occurrence. Accounting for such a worst corner case results in an overly pessimistic design. The Monte Carlo analysis technique is based on sampling the random variables from a known probability distribution, and performing repeated timing analysis on the sampled points. For reasonably accurate prediction of the probability distributions of a circuit, the method requires a static timing analysis step for each of the hundreds of thousands of sample points. This renders the Monte Carlo technique very inefficient and impractical to use for large circuits consisting of tens of thousands of gates.

In recent years, statistical static timing analysis (SSTA) has emerged as a promising and an efficient alternative to perform variation-aware timing analysis of a

circuit. The SSTA procedures can predict the timing yield of the circuit by extracting the probability distributions of the circuit delay. Most SSTA algorithms  $[CS05, VRK^+04, AMK^+05]$  achieve efficiency in their methods by assuming that the varying parameters can be accurately modeled by random variables following a Gaussian distribution. The normality assumption enables the use of closed form analytical expressions to evaluate the result of the basic statistical timing operations. However, not all parameters of variations can be accurately modeled as Gaussians. Moreover, the non-normal parameters exhibit statistical dependence arising from the spatial correlations in the circuit layout. Thus, in the presence of these correlated non-Gaussian parameters, the SSTA algorithms that assume normality can result in significant inaccuracies in estimating the probability distribution of a circuit. There have been some recent works, in the existing literature on SSTA, that extend the Gaussian SSTA algorithms to include non-Gaussian random variables [KS05, CZNV05]. However, these extensions are can only handle a few non-normal variables, and are not scalable to problems with large number of variables.

We present an efficient SSTA algorithm which is the first published work that can scalably handle a large number of correlated non-normal random variables in a reasonable runtime. We can efficiently handle the non-Gaussian parameters by employing an *independent component analysis* (ICA) technique [Bel, HO99, HO00, MP99], that enables us to achieve statistical independence between correlated non-Gaussian parameters. Using a moment-matching-based scheme we can extract the probability distribution function (PDF) and the cumulative distribution function (CDF) of all arrival time and delay random variables in an analytical closed-form expression. The time complexity of our SSTA procedure is  $O(n * N_G)$ , where *n* is the number of grids the chip layout is divided into, and  $N_G$  is the number of gates in the circuit, which is the same linear complexity as of the Gaussian SSTA algorithms. Our SSTA method can process as many as 256 correlated non-normal parameters in about 5 mins of runtime. We demonstrate the accuracy of our SSTA procedure by verifying it against Monte Carlo simulations. The average of the absolute errors of the proposed SSTA procedure, compared to Monte Carlo analysis, is 0.99% for  $\mu$ , 2.05% for  $\sigma$ , 2.33% for the 95% point, and 2.36% for the 5% quantile point of the circuit delay. An early version of this work was published in [SS06a].

### **1.3** Organization of the Thesis

The three research areas of power grid design, robust gate sizing and statistical timing analysis are each addressed in a separate chapter of this thesis. Chapter 2 comprises the algorithms for power grid design. In this chapter, Sections 2.6 and 2.7 contain the two proposed topology optimization solution techniques to design a high performance and a reliable power grid. Chapter 3 addresses the robust gate sizing problem, and consists of two formulations, explained in Sections 3.4 and **??**, to perform uncertainty-aware gate sizing. The problem of SSTA with non-Gaussian parameters is contained in Chapter 4. Finally, Chapter 5 summarizes the findings of this research thesis.

# Chapter 2 Power Grid Design Algorithms

### 2.1 Introduction to Power Grid Design

The network of interconnects, routed across multiple metal layers on the chip, that distribute the power supply and the ground to the logic gates on the chip is known as the power/ground (P/G) network or the supply network. Since, the P/G network electrically connects to all the devices on chip, its design has a big impact on the chip performance. Thus, the P/G distribution networks must be efficiently simulated, analyzed and optimized. The key constraints in the design of the P/G networks are those of:

- **IR drop:** The P/G networks consist of metal wires carrying currents. These wires offer resistance to the current flow, and hence a voltage drop occurs across them. Since the supply network is required to distribute power to all of the gates on the chip, large currents flow through these networks, and thus the voltage drop can be significant. This large voltage drop, along with the fact that the relentless push for low power has driven the supply voltage requirement below the 1 volt region [SIA05], drastically reduces the noise margins to maintain correct logic levels. Even if the drop is not large enough to cause logic inversion of voltage levels, it may still affect the performance of the chip by increasing the delays of logic gates as the current drive of the gates is proportional to the supply voltage.

- **Electromigration:** When current flows through the metal wires, the electrons collide with the metal atoms. These collisions result in a momentum transfer between conducting electrons and diffusing metal atoms to produce a force on the latter in the direction of electron flow. Over a period of time, the metal wires can become ruptured because of this collision force. This phenomenon of displacement of metal atoms due to the electron flux is known as electromigration (EM). The

problem of electromigration is a serious one in the P/G wires, since the currents always flow in one direction in these wires, i.e., from the  $V_{DD}$  nodes to the ground nodes. This problem is further aggravated due to the increase in current densities (defined as current per unit cross-sectional area of the wire) in the P/G wires because of the increase in the currents and the concomitant reduction in the wire widths due to technology scaling.

**Ground bounce due to inductive effects:** A sudden change of current flowing through a wire will induce abrupt voltage changes on that wire and its neighboring wires due to the inductance of the power grid. If these wires are a part of the on-chip P/G network, the induced voltage fluctuation is called the Ldi/dt noise. Due to this induced noise on the ground lines, today, we can no longer assume the existence of a universal ground node on the chip. The inductive noise or the ground bounce can cause severe signal integrity issues. Moreover the presence of inductance also leads to difficulties in the accurate analysis of P/G networks, e.g., the coupling capacitors between the power and ground lines now become floating capacitors and the Modified Nodal matrix [LC01] ceases to be diagonally dominant, which can lead to nonconvergence of iterative solvers.

As mentioned in Chapter 1, supply voltage fluctuations can be regarded as controllable type of variations. Employing some well-known power grid design techniques can directly control and reduce the voltage variations. To meet the constraints of IR drop and electromigration, the typical techniques available to the designers of supply networks are:

1. **Wire sizing:** By increasing the wire widths, the interconnect resistances are decreased and hence the IR drop is reduced. Increasing the widths also decreases the current density, and hence addresses the electromigration problem.

- 2. Adding decoupling capacitors (decaps): Decoupling capacitors are the on-chip capacitors that are deliberately added between the power grid and the chip substrate. The decaps act as charge reservoirs and maintain the required voltage levels within the clock cycle to prevent the dynamic or transient IR drop, also known as the voltage droop.

- 3. Using appropriate topologies for the P/G network: By optimizing the topology of the supply network, i.e., by "wisely" removing or adding wires in the supply grid or by optimal assignment of pads, it is possible to meet the voltage drop constraints.

In this chapter of the thesis, we present two topology optimization schemes to design a power grid which meets the static IR drop and the electromigration constraint. Using our power grid solution, a suitable decap placement scheme may be used, as a post-processing step, to safeguard against the transient voltage droop problem. Since we use a DC power grid analysis, our methods do not focus on the inductive noise in the P/G network. At an early stage of design, it is important to use simple models to efficiently optimize the power grid system. A more detailed transient simulation method may be employed later to analyze and reduce the inductive noise in the power grid wires.

#### 2.2 Previous Work

Most of the previous works in the area of P/G network design perform the design optimization by wire sizing and adding decoupling capacitors.

The methods of [TSL03,TS01,WC02,DMS89,WHC<sup>+</sup>01,BVGY01] all provide wire sizing schemes to design the P/G network. In [TS01, TSL03], equivalent circuit models of many series resistors in the original network is constructed, and then wire widths are optimized by transforming the constrained nonlinear programming to a sequence of linear programs. The problem is formulated by assuming the currents in segments to be

fixed, and representing the branch voltages as variables. An optimization scheme to calculate both the lengths and widths of P/G networks, using a sequential network simplex method is proposed in [WC02]. The authors of [DMS89] size the wires of P/G networks by building an optimization engine that first finds an initial feasible solution, and then iteratively looks for the optimal solution along a feasible direction, using a sensitivity analysis method. In [WHC<sup>+</sup>01], a wire sizing algorithm is proposed based on the conjugate gradient method and circuit sensitivity analysis. In this problem formulation, only the wire conductances are used as the variables and the adjoint method [PRV95] is used to calculate the gradient. A heuristic based on minimizing total wire area is developed in [BVGY01] that determines the optimal wire widths and the network topology, i.e., a tree or a mesh structure by solving a nonlinear convex optimization problem.

Schemes for optimal assignment of decoupling capacitors are presented in [SGS00, CL97, WMS05, ZPS<sup>+</sup>06]. A combined technique to appropriately size the wire widths and add decaps through a heuristic based on the transient adjoint sensitivity analysis is proposed in [SGS00]. In [CL97], a decap optimization procedure involving an iterative process of circuit simulation and floor planning is proposed. A multigrid-based approach to reduce the power grid system size is presented in [WMS05]. This method use a sequential quadratic programming method to optimize a cost function that adds decaps and performs wire sizing. Recently, in [ZPS<sup>+</sup>06], a decap budgeting algorithm, based on macromodeling was proposed.

The authors of [MK92, Cai88, OP98] all provide techniques for topology optimization of a power grid. In [MK92], a P/G network optimization method is provided by removal of selected wires. The problem is solves by formulating it as a nonlinear combinatorial optimization problem and relaxing some of the constraints. The wires are represented as conductance links between the nodes, and a decision variable vector is used to determine the presence or absence of these conductance links. Some other works in topology optimization [Cai88, OP98] address the problem of optimal pad assignment to the power/ground grid structures. The wire sizing and decap placement methods of [TSL03, WC02, TS01, DMS89, WHC<sup>+</sup>01, BVGY01, SGS00, CL97] all assume that the topologies of P/G networks are fixed, and only the widths of the wire segments, and the positions of decaps need to be determined. These techniques of power grid design by wire sizing and decap placement have a significant cost of over-utilization of the chip area. Furthermore, if the wire widths of the supply network vary throughout the chip, the routing of signal nets becomes much more difficult as a lot of book-keeping must be done to keep track of the locations and widths of P/G wires. In the works on topology optimization, the emphasis is on optimal assignment of the pins to the pads and placement of pads on the power grid. The fact that the topology has a significant influence on the final layout area is recognized, but the quest for a good topology design technique remains an open problem.

### 2.3 Proposed Power Grid Topology

In general, it is desirable to have as much regularity as possible in the power grid in order to permit the locations of power grid wires to be easily accounted for during signal routing. Furthermore, a regular grid structure can easily be analyzed [SG03] as it results in simpler circuit models. A highly irregular grid (for example, one that has been sized irregularly, or one in which wires have been selectively removed) may well provide an excellent solution if the power grid design problem is viewed in isolation. However, if we consider the *entire* design flow, a high degree of irregularity can be an impediment to the design methodology, as it may require a large amount of book-keeping to keep track of the precise locations of the power wires, and to determine which regions have excessive wiring congestion. Moreover, the number of optimizable parameters for such a problem can be very large, which may make the optimizable parameters and is ideal for the signal router. However, the constraint of full regularity can be overly limiting, since the requirement of regularity may cause the design to use excessive wiring resources. For instance, if all wire widths were to be required to be identical, the wires could be over-sized in regions that have relatively low current densities.

Our work proposes structured regularity in the power grid, with a topology that is intermediate to fully regular grids and highly irregular grids. These grids can be thought of as being a piecewise-uniform grid that is *globally irregular* and *locally regular*. This structure combines the best of both worlds: it has the advantages for faster routing that is afforded by fully regular nets, while offering the flexibility in optimization and better resource utilization permitted by irregular topologies. It is possible, in some cases, that due to the regularity in the grid structure, the number of tracks available for signal net routes in high congestion regions are insufficient. However, this aggravation of congestion arising due to a regular grid design, can be checked and controlled if such a problem is anticipated and accounted for in the grid design procedure. In [SHSN02], a procedure is developed to simultaneously design the supply grid, under voltage droop constraints, and the signal net, under congestion considerations. Starting from an initial dense regular grid, the non-critical power grid wires in the high congestion regions are removed followed by a heuristic wire sizing step to overcome the effects of wire removal. The resulting grid is irregularly sized and thus, loses the advantages of structured regularity.

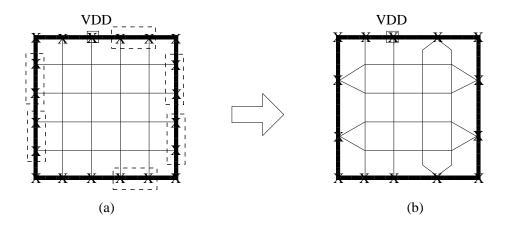

We use a toy example to illustrate the possible design choices for a power grid topology. For simplicity, let us assume that for the given example problem we can divide the chip into four rectangular regions or tiles having different current densities as shown in Figure 2.1(a).

The design in Figure 2.1(b) corresponds to the case where the voltage drop constraints are met by constructing a regularly structured grid with regularly sized elements with the same number of wires in the four tiles, i.e., four wires in each tile. This design uses more wire resources than required, since the wire sizes and the minimum number of wires in each tile are chosen according to the region with the worst-case voltage drop. The design in Figure 2.1(c) meets the design constraints by employing three wires in each tile but the wires in the upper half are sized individually and irregularly to decrease the resistance and reduce the voltage drop. Such a design makes the task of the signal router more difficult, since it must keep track of the variable amount of space available in each region. The design in Figure 2.1(d) utilizes the lowest wiring area by using variable pitches and by sizing individual wires separately. However, besides the fact that this design would make the routing of signal nets very difficult, the optimization itself involves numerous design variables and is therefore computationally intensive. The design in Figure 2.1(e) is essentially the design we propose and optimize in this work. This design is piecewise-uniform as within a tile it employs a near-constant pitch and uses the same wire sizing throughout the chip. The wires are sized uniformly throughout the chip so as to maintain regularity and meet the IR drop needs. Such a design is more economical in utilization of wiring resources than designs in Figure 2.1(b) and (c), and has the desirable property of regularity that Figure 2.1(d) lacks, and does not complicate the routing problem for signal nets. Moreover, due to an inherent structure in the design, it is easy to optimize.

Figure 2.1: (a) Current densities for an example chip that illustrates the possible choices for a power grid topology. Possible Designs of P/G Network (b) Grid with 4 wires in each tile and regular wire sizing. (c) Grid with 3 wires in each tile and irregular wire sizing. (d) A non-uniform grid with variable pitches throughout and irregular sizing. (e) A piecewise-uniform grid with 4 wires in the upper half tiles, 2 wires in bottom-left tile and 1 wire in bottom-right tile and uniform sizing.

In the following sections of this chapter, after discussing the power grid design preliminaries and hierarchical analysis method, two techniques are presented to design a locally regular, globally irregular power grid that meets the reliability constraints. The procedure in the first technique is based on an iterative sensitivity based heuristic optimization. The second power grid design technique uses the principles of hierarchical design and the property of locality.

## 2.4 Preliminaries

#### 2.4.1 Power Grid Circuit Model

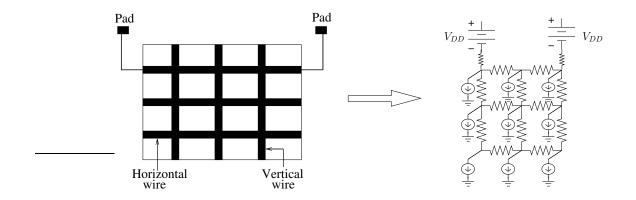

A power grid comprises metal wires running in the orthogonal directions and spanning multiple layers (typically, 5 to 8 for current microprocessor designs). The wires in two consecutive layers of metal are electrically connected to each other by using vias. The wires in the top-most metal layers are electrically connected to the  $V_{DD}$  pads that are located either on the peripheral power ring, as in the case for a chip with a wire-bond package, or are distributed over the entire chip area, using C4 bumps, as in the case of a flip-chip package. This system of pad connections and network of metal wires carrying currents from the  $V_{DD}$  pads to the underlying gates in the functional blocks, can be modeled as an equivalent electrical circuit comprising possibly millions of nodes. Under DC conditions, as illustrated in Figure 2.2, the power grid can be modeled as a resistive mesh, with the pads replaced by voltage sources. As seen in the figure, the wires are replaced by their equivalent resistances and the worst-case switching activities of the gates in the underlying functional blocks determines the loading currents.

Using the circuit model as shown in Figure 2.2, the branch resistance  $r_i$  of branch *i* can be expressed as:

$$r_i = \rho_s \frac{p}{w_i} \tag{2.1}$$

Figure 2.2: A power grid and its equivalent circuit model under DC conditions.

where  $\rho_s$  is the sheet resistivity,  $w_i$  is the width of the wire segment corresponding to the branch *i*, and *p* is the pitch of the power grid wires in the orthogonal direction, which is the same as the length of the wire segment. The pitch of the power grid wires could be different for different layers and in fact, may not even be constant for a given layer. After converting the voltage sources in the power grid model of Figure 2.2 to their Norton equivalents, the solution to the node voltages of the circuit is given by the following system of Modified Nodal Analysis (MNA) equations:

$$G \cdot \mathbf{V} = \mathbf{J}, \quad \mathbf{J}, \mathbf{V} \in \mathbb{R}^n, \quad G \in \mathbb{R}^{n \times n}$$

$$(2.2)$$

where n is the number of electrical nodes in the power grid circuit, G is the conductance matrix which contains stamps of all branch resistances, V is the vector of node voltages and J is a vector of load currents and the Norton currents of voltage sources.

For all nodes *j* and all branches *i* in the power grid circuit, the following constraints must be satisfied:

## 1. The IR drop constraint: $V_j > V_{spec}$

### 2. The current density or EM constraints : $|I_i| < \sigma w_i$

The voltage of node j is denoted as  $V_j$ , the branch current of branch i is denoted as  $I_i$ and  $\sigma$  is the specified current density for a fixed thickness (height) of the metal layer.

In the following sections of this chapter, we describe the design procedures for constructing a power grid that meets the two above constraints. The inputs to our power grid design problem are the number of power pads and their precise connection locations to the grid wires in the top layer, the placed functional blocks and an estimate of worst case currents drawn by the gates in the functional blocks. The amount of current drawn by each of the functional blocks can be determined by estimation techniques such as the ones proposed in [KNH95] and [WMR04]. Although, these methods extract time varying current waveforms, appropriate simplifications can be made to these techniques to estimate worst case steady state currents drawn by the functional blocks. We use the power grid circuit model as shown in Figure 2.2. Each node j in the power grid circuit is loaded by a constant current source  $c_j$ . Given the current estimate  $I_{f_k}$  drawn by a functional block k, and the physical coordinates of the placed functional block k, the values of constant current sources loading the power grid are chosen in such a way that the sum of all current sources at node locations lying over the functional block k add up to the functional block current  $I_{f_k}$ . The values of constant current sources and the functional block currents are expressed by the following relation:

$$\sum_{j \in \{\text{Nodes over block } k\}} c_j = I_{f_k}$$

(2.3)

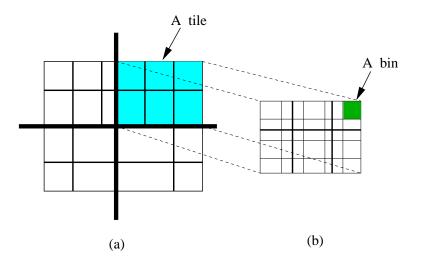

#### 2.4.2 Terminology

The following terminology would be adhered to in this chapter of the thesis. A *tile* or a *partition* is a rectangular region of the chip and the chip is divided into many tiles or partitions. A *skeleton grid* is an imaginary grid with wires running in orthogonal directions which is superimposed over the entire chip area. This skeleton grid which is a uniform and a continuous grid of constant pitch is a place-holder for adding the wires. The concept of the skeleton grid is explained in Section 2.6. An electrical node in a tile having links to other nodes in the same tile is called an *internal node*, the nodes at the edges of tiles that connect a tile to its neighboring tiles are called *port nodes* and the

nodes corresponding to the  $V_{DD}$  or ground pads are treated as global nodes.

# 2.5 Circuit Analysis by Macromodeling

To detect the nodes and branches in the power grid circuit which violate the IR drop and EM constraints, our iterative power grid optimization algorithms use an explicit power grid analysis step in each iteration. For the purposes of determining the most critical nodes and branches in the circuit, our work uses the hierarchical circuit analysis technique of [ZPS<sup>+</sup>00]. This section discusses the adaptation of the macromodeling method to our work.

As will be explained in Sections 2.6 and 2.7, both of our proposed power grid design schemes employ a method of dividing the large power grid area into smaller rectangular regions, referred to as partitions or tiles, and designing the subgrids locally in these smaller regions. In such a scenario of working with the partitions of a power grid system, the hierarchical modeling idea can be efficiently applied to our power grid systems.

Referring to the MNA Equation of (2.2), and splitting the system into internal nodes and port nodes, we can rewrite the system of equations as:

$$\begin{bmatrix} G_{aa} & G_{ab} \\ G_{ab}^T & G_{bb} \end{bmatrix} \begin{bmatrix} \mathbf{V_a} \\ \mathbf{V_b} \end{bmatrix} = \begin{bmatrix} \mathbf{J_a} \\ \mathbf{J_b} + \mathbf{I} \end{bmatrix}$$

(2.4)

where

- V<sub>a</sub> and V<sub>b</sub> are the vector of the voltages at the internal nodes and the port nodes, respectively.

- J<sub>a</sub> and J<sub>b</sub> are the vectors of current sources connected at the internal nodes and the ports, respectively.

- I is the vector of currents through the interfaces between the ports.

- $G_{ab}$  is the conductance of links between the internal nodes and the ports.

- *G<sub>aa</sub>* is the conductance matrix corresponding to the connections only between the internal nodes.

- *G*<sub>bb</sub> is the conductance matrix corresponding to the connections only between the port nodes.

As we are employing a resistive mesh model and DC excitations, each rectangular tile can be abstracted as a multiport electrical element which has a linear current-voltage relationship. These multiport elements are referred to as *macromodels*. If m is the number of wires in the horizontal direction in a tile and n is the number of vertical wires in a tile, each macromodel can be regarded as a q-port linear element, where q = 2(m + n), with its transfer characteristic given by the following equation:

$$\mathbf{I} = A\mathbf{V} + \mathbf{S} \tag{2.5}$$

where  $\mathbf{I} \in \mathbf{R}^{q}$ ,  $A \in \mathbf{R}^{q \times q}$ ,  $\mathbf{V} \in \mathbf{R}^{q}$ ,  $\mathbf{S} \in \mathbf{R}^{q}$ , A is the port admittance matrix,  $\mathbf{V}$  is the vector of voltages at the ports, corresponding to the voltages at the nodes on edges of the tiles,  $\mathbf{I}$  is the current through the interface between the tiles, and  $\mathbf{S}$  is a vector of current sources between each port and ground.

Referring to the matrix algebra, explained in detail in [ZPS<sup>+</sup>00], the macromodel elements, the admittance matrix A, and the current source vector **S**, can be derived from the following relations:

$$A = L_{bb} L_{bb}^{T}$$

$$\mathbf{S} = L_{ba} L_{aa}^{-1} \mathbf{J}_{\mathbf{a}} - \mathbf{J}_{\mathbf{b}}$$

(2.6)

where  $L_{aa}$ ,  $L_{ba}$ , and  $L_{bb}$  represent the submatrices of the Cholesky factor matrix L, of the conductance matrix G, with indices a and b, corresponding to the internal nodes, and the ports, respectively.

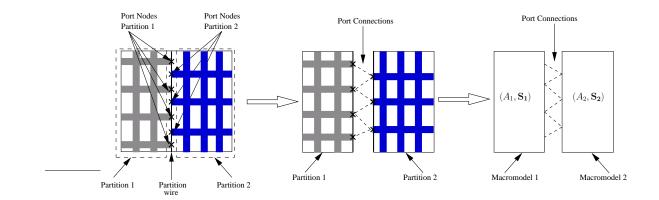

Figure 2.3 shows the conversion of tiles of the power grid into macromodels. In this example, the power grid which is divided into 9 tiles, is reduced to a system of nine

Figure 2.3: Converting the P/G network to a system of macromodels. (a) A P/G network with port nodes at the tile boundaries. (b) The P/G network changed to a system of macromodels connected to each other through the port nodes.

multiport elements given by the macromodel parameters  $(A, \mathbf{S})$ . The macromodels are connected to each other through port connections.

The macromodel parameters (A, S) of each tile are stamped into the MNA equation in the global system given by

$$M\mathbf{X} = \mathbf{b} \tag{2.7}$$

where

- *M* is the matrix containing the conductance links between global nodes and the tiles, the conductance links between the tiles, and the stamps of *A* for each tile.

- X is the vector of voltages of global nodes and ports.

• **b** is the vector of current sources at global nodes and stamps of **S** for each tile.

The above Equation (2.7) is solved, either using a direct solver (as for the first power grid design scheme) or by using an iterative solver (as for the second power grid design procedure), to determine the global node and port voltages. If it is required to solve for the voltages of the internal nodes of any tile or partition, the elements of the interface current vector I are determined by Equation (2.5), and are fed back into Equation (2.4), which is then solved by a direct solver by reusing the Cholesky factors, and performing backward substitution of the already determined elements of the port voltage vector  $V_b$ .

Since in our optimization procedures, while designing local power grids, only a few tiles or partitions are required to be processed in any iteration, the power grid system solution by hierarchical analysis proves very efficient. For the purposes of efficiency, we also use the step of sparsification of A matrix as proposed in [ZPS<sup>+</sup>00]. This increases the sparsity of the global matrix M at the cost of reasonable simulation errors.

## 2.6 Solution Technique 1: A Sensitivity-based Heuristic