# DELAY MODELING AND OPTIMIZATION IN VLSI CIRCUIT SYNTHESIS

#### A THESIS

# SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA

BY

#### MAHESH KETKAR

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Sachin S. Sapatnekar, Advisor JULY 2002

## UNIVERSITY OF MINNESOTA

This is to certify that I have examined this copy of a doctoral thesis by

#### MAHESH KETKAR

and have found that it is complete and satisfactory in all aspects, and that any and all revisions required by the final examining committee have been made.

| Professor Sachin S. Sapatnekar |

|--------------------------------|

| Name of Faculty Advisor        |

|                                |

|                                |

| Signature of Faculty Advisor   |

|                                |

|                                |

| Date                           |

GRADUATE SCHOOL

# **Abstract**

The evolution of deep submicron technologies has placed a high importance on the fidelity of simulation and modeling techniques as compared to the final chip realization. In addition, ever tightening delay, area, and power constraints together with increasing design complexities demand that the optimization techniques used in design process be fast and accurate. The purpose of this thesis is to develop accurate delay models that are amenable to optimization and to develop efficient yet accurate synthesis and optimization strategies at logic, circuit, and physical levels of design process. The thesis consists of three parts that are described below.

A large number of the optimizations that arise in electronic design automation can be modeled as nonlinear optimization problems, which can be solved more easily if the objective and constraint functions are convex. Particularly for delay optimization, this is becoming increasingly problematic since the existing models that possess such properties, such as the Elmore delay model, have become highly inaccurate in deep submicron technologies. Therefore, the first part of this thesis involves development of accurate and convex models for gate delay. The efficacy of the model is shown by its incorporation into various optimizers and performing area-delay and dynamic power-delay trade-off optimizations.

Another important issue that has arisen in the recent technology generations is that, gate leakage has become a significant contributor to the total power. The reason for this is that the subthreshold leakage current of a transistor has an exponential dependence on its threshold voltage  $(V_t)$ , which no longer scales in proportion to the supply voltage. Hence, the second part of this thesis targets leakage-delay optimization in contrast to the dynamic power-delay optimization formulation used in the first problem. A novel enumerative approach, along with efficient pruning techniques, is proposed for  $V_t$  assignment to minimize power under delay constraints. This method is then used in a unified approach employing simultaneous transistor sizing and threshold voltage assignment to achieve a low leakage circuit configuration under given area and delay constraints.

The third part of this thesis develops a methodology for efficient timing closure for dat-

apath dominated circuits, and involves logic synthesis guided by structural properties of the circuit. Datapaths are typically characterized by a high degree of regularity, and it is beneficial to preserve this regularity during synthesis so that layout synthesis tools can generate regular, and hence predictable layouts. However, the rigid preservation of regularity is likely to result in circuit configurations with high delay values. The approach proposed involves controlled destruction of regularity during the synthesis process, thus leading to delay-optimized, yet highly regular, circuits.

# Acknowledgement

First, I would like to thank my advisor, Prof. Sachin Sapatnekar, for his guidance and support throughout my doctoral studies. He provided very valuable help whenever I needed assistance of any kind. His emphasis on reasoning out everything, on clarity in presentation of ideas, and on looking at the holistic picture of a problem always guided me in the right direction, and will continue to guide me throughout my career.

I would like to thank Prof. Bazargan, Prof. Sobelman, and Prof. Du, for reviewing this thesis and for providing valuable suggestions. I would like to thank Dr. Priyadarsan Patra from Intel Corporation, for his valuable guidance throughout my doctoral work.

I would also like to thank members of the VEDA Lab - Brent, Cheng, Haihua, Haitian, Rupesh, Suresh, Tianpei, and Venkat - with whom I have had several meaningful discussions. I would like to thank Dr. Jiang Hu and Dr. Min Zhao for their help during early period of my doctoral studies, and to Arvind Karandikar for his help in various aspects of software development. I would like to thank Kishore Kasamsetty for his contributions in the project on gate delay modeling.

In four years I met a lot of interesting people who made my stay in Minneapolis a very enjoyable experience, and to that effect, I would like to thank Girish, Parag, Ameeta, Sirisha, Rupa, Kedar, and Cristi. Special thanks are due to Shantanu Rane, a great roommate and a close friend, for his support, and for various stimulating conversations.

Finally, I would like to thank my parents for their continuous support and encouragement during this work, and for their teachings throughout my life. This thesis would not have taken place without them.

# Contents

| 1 Introduction |     |        | 1                                |    |

|----------------|-----|--------|----------------------------------|----|

|                | 1.1 | Introd | uction                           | 1  |

|                | 1.2 | Thesis | organization                     | 5  |

| 2              | Pre | limina | ries                             | 6  |

|                | 2.1 | Circui | t parameters                     | 6  |

|                |     | 2.1.1  | Area                             | 7  |

|                |     | 2.1.2  | Delay                            | 7  |

|                |     | 2.1.3  | Power                            | 7  |

|                | 2.2 | Elmor  | e delay model                    | 8  |

|                | 2.3 | Transi | stor sizing problem              | 10 |

|                | 2.4 | Nonlin | near optimization                | 10 |

|                | 2.5 | Geome  | etric optimization               | 11 |

|                |     | 2.5.1  | Posynomial functions             | 11 |

|                |     | 2.5.2  | Geometric programming            | 11 |

|                | 2.6 | Conve  | x optimization                   | 12 |

|                |     | 2.6.1  | Convex sets and convex functions | 12 |

|                |     | 2.6.2  | Convex programming problem       | 13 |

|                | 2.7 | Mixed  | integer nonlinear programs       | 14 |

| 3              | Cor | ıvex D | elay Modeling                    | 16 |

|   | 3.1                      | Introduction                                                                                                                                                                                                                                                       | 16                                                 |

|---|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|   | 3.2                      | Existing delay modeling approaches                                                                                                                                                                                                                                 | 16                                                 |

|   | 3.3                      | Generalized posynomials                                                                                                                                                                                                                                            | 18                                                 |

|   |                          | 3.3.1 Definitions                                                                                                                                                                                                                                                  | 18                                                 |

|   |                          | 3.3.2 Proof of convexity                                                                                                                                                                                                                                           | 19                                                 |

|   | 3.4                      | Delay modeling using generalized posynomials                                                                                                                                                                                                                       | 22                                                 |

|   |                          | 3.4.1 Characterization of a set of primitives                                                                                                                                                                                                                      | 24                                                 |

|   | 3.5                      | Modeling Results                                                                                                                                                                                                                                                   | 30                                                 |

|   | 3.6                      | Conversion of generalized posynomials to posynomials                                                                                                                                                                                                               | 32                                                 |

|   | 3.7                      | Circuit optimization incorporating the new delay model                                                                                                                                                                                                             | 34                                                 |

|   |                          | 3.7.1 Proof of convexity of path delays                                                                                                                                                                                                                            | 35                                                 |

|   |                          | 3.7.2 Area – delay trade-off optimization                                                                                                                                                                                                                          | 37                                                 |

|   |                          | 3.7.3 Dynamic power – delay trade-off optimization                                                                                                                                                                                                                 | 38                                                 |

|   |                          | 3.7.4 Introduction of intermediate variables                                                                                                                                                                                                                       | 40                                                 |

|   | 3.8                      | Conclusion                                                                                                                                                                                                                                                         | 42                                                 |

|   |                          |                                                                                                                                                                                                                                                                    |                                                    |

| 4 | Lea                      | kage – Delay Trade-off Optimization                                                                                                                                                                                                                                | 43                                                 |

| 4 | <b>Lea</b> 4.1           | kage - Delay Trade-off Optimization                                                                                                                                                                                                                                | <b>43</b> 43                                       |

| 4 |                          |                                                                                                                                                                                                                                                                    |                                                    |

| 4 | 4.1                      | Introduction                                                                                                                                                                                                                                                       | 43                                                 |

| 4 | 4.1<br>4.2               | Introduction                                                                                                                                                                                                                                                       | 43<br>44                                           |

| 4 | 4.1<br>4.2<br>4.3        | Introduction                                                                                                                                                                                                                                                       | 43<br>44<br>47                                     |

| 4 | 4.1<br>4.2<br>4.3        | Introduction                                                                                                                                                                                                                                                       | 43<br>44<br>47<br>49                               |

| 4 | 4.1<br>4.2<br>4.3        | Introduction                                                                                                                                                                                                                                                       | 43<br>44<br>47<br>49                               |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Introduction                                                                                                                                                                                                                                                       | 43<br>44<br>47<br>49<br>49<br>50                   |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                              | 43<br>44<br>47<br>49<br>49<br>50                   |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Introduction          Previous work          Problem formulation          Leakage and delay estimation          4.4.1 Leakage estimation          4.4.2 Delay estimation          Dual $V_t$ assignment          4.5.1 Algorithm                                   | 43<br>44<br>47<br>49<br>49<br>50<br>51<br>52       |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Introduction          Previous work          Problem formulation          Leakage and delay estimation          4.4.1 Leakage estimation          4.4.2 Delay estimation          Dual $V_t$ assignment          4.5.1 Algorithm          4.5.2 Pruning techniques | 43<br>44<br>47<br>49<br>49<br>50<br>51<br>52<br>55 |

|   |     | 4.6.2 Algorithm                         | 60 |

|---|-----|-----------------------------------------|----|

|   |     | 4.6.3 Postprocessing                    | 61 |

|   | 4.7 | Implementation and results              | 61 |

|   | 4.8 | Conclusion                              | 65 |

| 5 | Syn | thesis of Datapath-Dominated Circuits   | 66 |

|   | 5.1 | Introduction                            | 66 |

|   | 5.2 | Motivation                              | 69 |

|   | 5.3 | Circuit regularity                      | 71 |

|   |     | 5.3.1 Regularity modeling               | 71 |

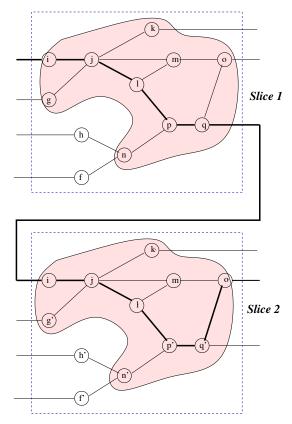

|   |     | 5.3.2 Regularity extraction             | 73 |

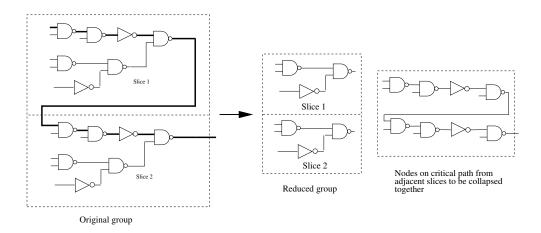

|   | 5.4 | Synthesis approach                      | 76 |

|   |     | 5.4.1 Slice synthesis                   | 76 |

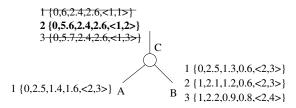

|   |     | 5.4.2 Controlled regularity destruction | 77 |

|   | 5.5 | Implementation and results              | 81 |

|   | 5.6 | Conclusion                              | 82 |

| 6 | Coı | aclusion and future research directions | 83 |

# List of Figures

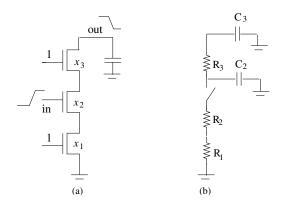

| 2.1 | Elmore delay model                                                                | 9  |

|-----|-----------------------------------------------------------------------------------|----|

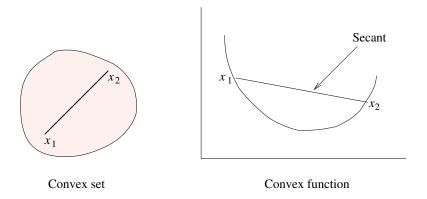

| 2.2 | Convex set and convex function                                                    | 13 |

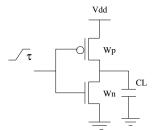

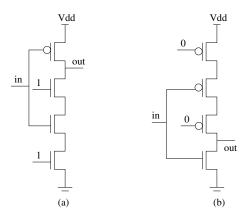

| 3.1 | Inverter circuit                                                                  | 22 |

| 3.2 | Inaccurate mapping of a NAND gate                                                 | 25 |

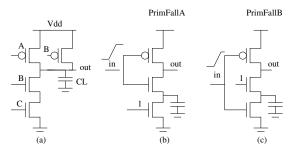

| 3.3 | Two-input primitives for fall transition                                          | 26 |

| 3.4 | Three-input primitives                                                            | 27 |

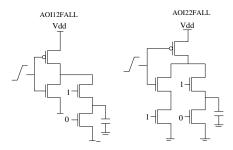

| 3.5 | Examples of AOI Primitives                                                        | 28 |

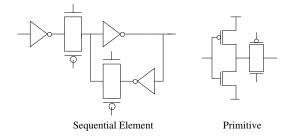

| 3.6 | Sequential Element and Primitive                                                  | 29 |

| 3.7 | Primitive validation                                                              | 30 |

| 3.8 | Validation of a 2-input NAND gate                                                 | 32 |

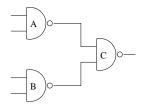

| 3.9 | An example circuit                                                                | 40 |

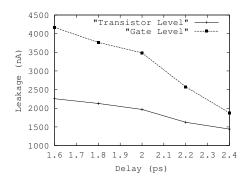

| 4.1 | Transistor-level versus gate-level $V_t$ assignment for C2670                     | 44 |

| 4.2 | Pseudocode for $V_t$ assignment                                                   | 53 |

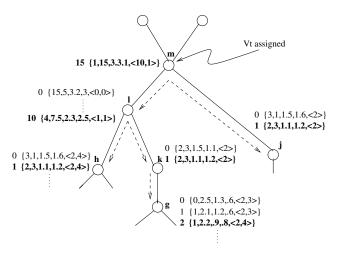

| 4.3 | Enumeration for $V_t$ assignment                                                  | 54 |

| 4.4 | Input dominance                                                                   | 58 |

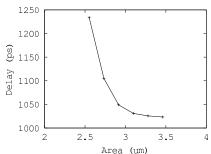

| 4.5 | Delay-area curve of C499 demonstrating the knee region                            | 59 |

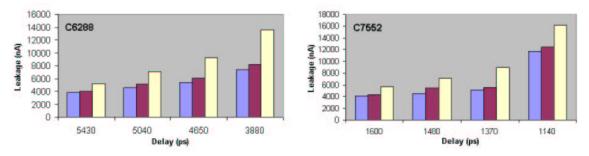

| 4.6 | Comparison of $V_t$ assignment at transistor-level, stack-level, and gate-level . | 64 |

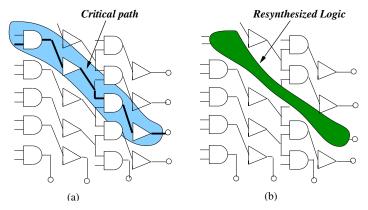

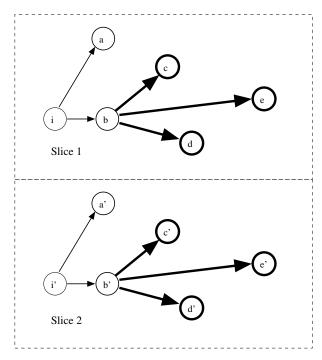

| 5.1 | Trading off circuit regularity for delay reduction                                | 68 |

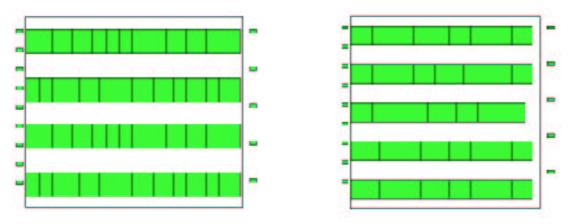

| 5.2 | Layout of synthesized adders                                                      | 71 |

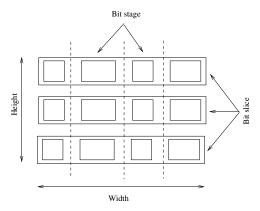

| 5.3 | Circuit regularity                    | 72 |

|-----|---------------------------------------|----|

| 5.4 | Regularity signature                  | 74 |

| 5.5 | Regularity extraction                 | 76 |

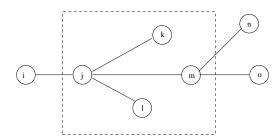

| 5.6 | Collapsing nodes from adjacent slices | 78 |

| 5.7 | Node selection for resynthesis        | 80 |

# List of Tables

| 3.1 | Primitive Validation                                                     | 30 |

|-----|--------------------------------------------------------------------------|----|

| 3.2 | Gate Validation                                                          | 31 |

| 3.3 | Comparison of Model Delay for C17 with SPICE                             | 33 |

| 3.4 | Results of area-delay tradeoff optimization                              | 38 |

| 3.5 | Results of power-delay tradeoff optimization                             | 41 |

| 4.1 | Dual $V_t$ assignment using PB algorithm [1] and the proposed algorithm  | 62 |

| 4.2 | Optimization results, comparing the performance of SBA [2] and MinSATVA. | 63 |

| 5.1 | Comparison of synthesis results                                          | 81 |

# Chapter 1

# Introduction

#### 1.1 Introduction

For the past four decades, the semiconductor industry has distinguished itself by the rapid pace of improvements in its products. The propelling force behind this magnificent journey has been an ambition to adhere to Moore's Law [3], which originally stated that the number of devices on a chip would double every year (the time frame was later modified to every two years, and subsequently averaged to every eighteen months).

Thus each new generation of chips has more and more devices and hence interconnects as compared to previous generations. At the same time, market competition and widespread use of mobile devices, has resulted in ever tightening delay, area, and power constraints. These together have led to a drastic increase in design complexity, which means that the automatic synthesis tools must do a better job of optimization; specifically, the tools should realize good circuit configurations in as little time as possible. This requirement translates down to various issues in development of CAD tools, and some of these are mentioned below.

- It dictates that the CAD tools should be scalable to handle larger and more complex designs as compared to previous generations.

- It warrants better fidelity of area, delay, and power models to actual silicon realiza-

tions, and that the models should be amenable to optimization so that accurate global solutions can be found.

- The advances in process technology typically come with a host of new design variables and hence a new set of challenges for the designers. One example of this is the increased relative importance of newer design considerations such as leakage power as compared to previous generations. CAD tools are required to handle such new design parameters.

- It prompts the exploration of radical shifts in design methodologies to minimize synthesis times and to obtain good solutions.

The research in this thesis tries to address timing optimization of VLSI circuits in light of some of the issues mentioned above. The three problems solved in this thesis are listed below, and their relation to the issues mentioned above is examined following the enumeration.

- Development of convex and accurate models for the gate delay. The models are incorporated into optimization engines to solve area-delay and power-delay tradeoffs.

- Optimization of standby leakage power under area and delay constraints utilizing transistor sizing and dual threshold voltage assignment.

- Regularity-driven synthesis of datapath dominated circuits.

The underlying theme in the choice of the problems solved is delay optimization. The first problem is targeted towards development of delay models that will lead to fast and accurate solution of a transistor sizing problem. The problem tries to address the issue of modeling mentioned above, and at the same time has repercussions on scalability, because the existence of optimization-amenable models can enable fast and accurate optimizations with proper choice of optimization engine. The second problem provides an algorithm for the optimization of leakage-delay trade-offs and thus addresses an important emerging issue. The third part presents a methodology that improves upon the traditional synthesis flow in that it uses physical information to drive the logic synthesis process.

The material presented below provides an introductory treatment of these problems and gives an insight into the choice of these particular problems in the arena of timing optimization. It also provides numerical figures to highlight the contributions of this thesis.

Before embarking on the introduction of individual problems it is in order to see where these problems fit in a typical design flow, which consists of various stages [4]. Such a flow ranges from behavioral and architectural synthesis at the topmost level, which determines an assignment of circuit functions to various operators, their interconnection, and execution timing, to layout synthesis at the bottommost level, which converts a netlist of transistors into a geometric representation to be realized in silicon. This thesis concentrates on circuit synthesis problems arising at lower levels of abstraction, namely, the logic, circuit, and physical levels.

Let us consider the motivation for the first problem. A large number of the optimizations that arise at the circuit and physical levels can be modeled as nonlinear optimization problems, which can be solved more easily if the objective and constraint functions have the property of convexity, which is defined precisely in Section 2.6.1, and numerous optimizations have been facilitated by the fact that the Elmore delay model [5] can be proved to be a convex function in some design variables. Unfortunately, the value of this property has been diminished as the Elmore has become highly inaccurate in deep submicron technologies. Therefore, the first issue addressed in this thesis involves the development of accurate and convex models for gate delay. A new class of convex functions called generalized posynomials is proposed and subsequently used to accurately model the gate delay. Experimental results showed that the delay values obtained using the proposed models were within 5% of SPICE [6] on average, and within 2% of SPICE for most of the gates. The efficacy of the model is shown by incorporating it into various optimizers and performing area-delay and dynamic power-delay trade-off optimizations.

It is well known that in the past, trends in performance, density and power have followed the scaling theory. For these trends to continue, two important issues that need special attention are power delivery and power dissipation [7]. Typically, each generation of chips has shown about 30% reduction in gate delay and about the same or greater reduction in energy dissipation per transition. The total power dissipation can be scaled down by reducing either the supply voltage, frequency or die size, each of which results in reduced performance. Therefore, the problem of optimization for low power to meet the stringent performance constraints continues to be a very important problem.

Recognizing this, power-delay trade-off optimizations are addressed in two of the problems solved in this thesis. The power dissipation of a gate results from three sources, namely, dynamic power, leakage power, and short circuit power, described in detail in Section 2.1.3. Power optimization is addressed in part in the first problem, by incorporating the new delay model into an optimization engine to solve the problem of trading-off dynamic power with delay.

In recent generations, however, the gate leakage has become a significant contributor to the total power. The reason for this is that the subthreshold leakage current of a transistor has an exponential dependence on its threshold voltage  $(V_t)$ , which no longer scales in proportion to the supply voltage from one generation to the next. Hence, the second problem targets the trade-off optimization between leakage power and delay, in contrast to the dynamic power-delay optimization formulation used in the first problem. A novel enumerative approach, along with efficient pruning techniques, is proposed for  $V_t$  assignment to minimize power under delay constraints. This method is then incorporated into an unified approach employing simultaneous transistor sizing and threshold voltage assignment to achieve a low leakage circuit configuration under given area and delay constraints. Results show that the  $V_t$  assignment algorithm on average results in 50% reduction in leakage power at fixed transistor sizes as compared to an existing approach [1]. The unified approach resulted in 9% lower leakage on average, and barring two small ISCAS 85 benchmark circuits, performed about 1.4x faster as compared to an existing unified optimization approach [2].

The third part of this thesis is related to the interaction between logic synthesis and layout. It develops a methodology for efficient timing closure of datapath-dominated circuits, and involves logic synthesis guided by structural properties of the circuit. Datapaths

are characterized by regularity (explained in Section 5.2). It is beneficial to preserve this regularity during synthesis so that layout synthesis tools can generate regular and hence predictable layouts. However, the rigid preservation of regularity typically results in circuit configurations with high delay values. The approach proposed involves controlled destruction of regularity during the synthesis process, thus leading to delay-optimized, yet highly regular circuits. The experimental results show that the proposed methodology realizes circuits with about the same delays and much higher regularity, as compared to the circuits obtained by traditional synthesis.

# 1.2 Thesis organization

The organization of this thesis is as follows. Chapter 2 presents background material relevant to this thesis, including a brief treatment of mathematical optimization. Chapter 3 describes a solution to the first problem, introducing a new class of convex functions and demonstrating its use in gate delay modeling. The delay model is incorporated into various optimization engines and the results of area-delay and dynamic power-delay tradeoff optimizations are provided. Next, an algorithm for leakage power optimization via transistor sizing and  $V_t$  assignment is presented in Chapter 4, corresponding to a solution to the second problem in the thesis. The third problem is tackled in Chapter 5 which develops a method for regularity-driven synthesis of datapath-dominated circuits. Finally, Chapter 6 provides concluding remarks and future research directions.

# Chapter 2

# **Preliminaries**

Two of the problems tackled in this thesis involve optimization of design variables, and hence it is in order to begin by presenting some introductory material on mathematical optimization. Most of the circuit optimization problems pertain to one specific category of optimization problems: nonlinear optimization. Transistor sizing, a problem from circuit synthesis, is used repeatedly in this thesis, and is also used as a running example throughout explanation of optimization categories. To give an idea of the transistor sizing problem, various circuit parameters are first introduced in Section 2.1. The explanation also serves the purpose of introducing the models used in this thesis. In particular, the Elmore model is explained in detail in Section 2.2, and following that the transistor sizing problem is introduced in Section 2.3. Nonlinear optimization is then introduced in Section 2.4, while three special types of nonlinear optimization problems, namely, geometric programs, convex programs, and mixed integer nonlinear programs, are introduced in Sections 2.5, 2.6, and 2.7, respectively.

# 2.1 Circuit parameters

An integrated circuit can be represented at various levels of abstractions such as the circuit level, the logic level, or the architectural level. At each level of abstraction, circuit parameters are estimated using different models, and the accuracy of these models typically

decreases as one moves to a higher level of abstraction. The first two problems tackled in this thesis involve circuit-level optimizations, and this section provides the models used at this level.

#### 2.1.1 Area

The area of a transistor netlist is typically measured as summation of transistor widths:

$$Area = \sum_{i=1}^{n} x_i \tag{2.1}$$

where n is the number of transistors in the circuit, and  $x_i$  represents the size of the  $i^{th}$  transistor in the circuit. This area model does not consider the routing area, but this is acceptable in case of transistor sizing, which makes but little perturbations to circuit placement, and in case of threshold voltage  $(V_t)$  assignment, which does not necessitate any alterations in placement.

#### 2.1.2 Delay

The delay characteristics of the output waveform at a gate may be represented by two numbers:

- (1) the *delay*, i.e., the difference in the time when the output waveform crosses 50% of its final value, and the corresponding time for the input waveform.

- (2) the *output transition time*, i.e., the time required for the waveform to go from 10% to 90% of its final value.

The Elmore delay model, described in the next section, models the gate delay.

#### 2.1.3 Power

The power dissipated in a gate consists of three components.

(1) Dynamic power: This refers to the power dissipated in a gate when it switches from one logic state to another. This component of power dissipation is due to the charging and

discharging of the output capacitance, and is given by

$$P_{i_{sw}} = \frac{1}{2} \cdot V_{dd}^2 \cdot C_i \cdot TD_i \tag{2.2}$$

where  $P_{i_{sw}}$  is the average switching power dissipation,  $V_{dd}$  is power supply voltage,  $C_i$  is the output capacitance, and  $TD_i$  (explained later in Section 3.7.3) is the transition density, all corresponding to gate  $n_i$ .

(2) Leakage power: This component corresponds to the power dissipated by the current that flows through a transistor that is nominally off and is caused by two mechanisms. The first is the subthreshold leakage, which forms the dominant source of leakage power, and the second part is due to the tunneling current through the gate oxide. The BSIM [8] model for the subthreshold leakage current for a single transistor is listed below.

$$I_{leak} = I_o e^{(V_{gs} - V_t)/nV_{therm}} (1 - e^{-V_{ds}/V_{therm}}),$$

where  $I_o = \mu_0 C_{ox}(W/L) V_{therm}^2 e^{1.8}$  (2.3)

Here  $\mu_0$  is the zero bias electron mobility, n is the subthreshold slope coefficient,  $V_{gs}$  and  $V_{ds}$  are the gate-to-source voltage and the drain-to-source voltage, respectively,  $V_{therm}$  is the thermal voltage, and W and L are the transistor width and length, respectively.

(3) Short circuit power: When the output of a gate switches, a low resistance path exists between  $V_{dd}$  and ground during the period of the input transition, and this leads to short circuit power dissipation. Short circuit power forms a very small component of the total power provided the transition times are all controlled, and hence is not considered as an optimization parameter in this thesis. Interested reader can find further treatment of short circuit power in [9].

# 2.2 Elmore delay model

An RC network is a collection of resistances and capacitances. Elmore [5] proposed that the delay of an RC network under a step input can be reasonably estimated as the time coordinate of the center-of-area of the impulse response curve. To use this model to estimate the delay of a gate, the gate is converted into a network of resistances and capacitances, as shown in Figure 2.1. Figure 2.1(a) shows a switching gate with transistors of sizes  $x_1$ ,  $x_2$  and  $x_3$ , and its equivalent Elmore model is shown in Figure 2.1(b).

Figure 2.1: Elmore delay model

The delay of the gate is then evaluated as the Elmore time constant of this RC network, given as

$$(R_1 + R_2)C_2 + (R_1 + R_2 + R_3)C_3 (2.4)$$

Each  $R_i$  is inversely proportional to the transistor width  $x_i$ , and each  $C_j$  is directly proportional to transistor width  $x_i$ . Hence Equation (2.4) can be rewritten as

$$(A/x_1 + A/x_2)(Bx_2 + Cx_3 + D) + (A/x_1 + A/x_2 + A/x_3)(Bx_3 + E)$$

(2.5)

where A, B, and C are constant coefficients for the resistance, drain capacitance, and source capacitance, respectively, of a unit size transistor, and D and E are wire capacitances.

Thus the general form of the Elmore delay can be written as

$$D(\mathbf{x}) = \sum_{i,j=1}^{n} a_{ij} \frac{x_i}{x_j} + \sum_{i=1}^{n} \frac{b_i}{x_i} + K$$

(2.6)

where  $a_{ij}, b_i, K \in \mathbf{R}^+$  are constants and,  $\mathbf{x} = [x_1, \dots, x_n]$  is the vector of transistor sizes.

This form is used in various published works on transistor sizing, for example, in TILOS [10] and iCONTRAST [11]. A detailed treatment of timing analysis using the Elmore model can be found in [12].

## 2.3 Transistor sizing problem

Increasing the width of a transistor results in an increase in the circuit area and power dissipation. Moreover, if the updated transistor is an nmos transistor and lies on the resistive path between input  $a_i$  and the output of the gate, then it has two effects on the gate delay:

- (1) it results in reduced delay from  $a_i$  to output for the falling output transition, and

- (2) it leads to increased delay from  $a_i$  to output for the rising output transition.

Hence determining the widths of transistors in a circuit involves carefully solving this tradeoff. Transistor sizing has been traditionally been formally defined as [10]:

minimize Area or Power

subject to

$$Delay \leq T_{spec}$$

. (2.7)

Previous works on the use of transistor sizing for area-delay trade-off optimization and power-delay trade-off optimization are outlined in Sections 3.7.2 and 3.7.3, respectively.

# 2.4 Nonlinear optimization

A Nonlinear Program (NLP) is a problem that can be formulated as

minimize

$$f(x)$$

subject to

$$g_i = 0, \quad 1 \le i \le k$$

$$h_j \ge 0, \quad k+1 \le j \le m$$

$$(2.8)$$

where f(x),  $g_i$  and  $h_j$  are all nonlinear functions, and k is the number of equality constraints and m is the number of total constraints. Since, the functions are nonlinear, finding a global minimum of the optimization problem is a very difficult task, and there is always the danger that a solution technique may be trapped in a local minimum.

However, not all nonlinear programs are difficult to solve. The objective functions and constraints may possess certain properties that can be exploited to efficiently obtain a global solution. Two of such problems are the *geometric programming* and the *convex programming* problems, which are explained in the next two sections.

### 2.5 Geometric optimization

#### 2.5.1 Posynomial functions

A posynomial is a function p of a positive variable  $\mathbf{x} \in \mathbb{R}^n$  that has the form

$$p(\mathbf{x}) = \sum_{j} \gamma_{j} \prod_{i=1}^{n} x_{i}^{\alpha_{ij}}$$

(2.9)

where the exponents  $\alpha_{ij} \in \mathbf{R}$  and the coefficients  $\gamma_j \in \mathbf{R}^+$ . In the positive orthant in the  $\mathbf{x}$  space, posynomial functions have the useful property that they can be mapped onto a convex function (explained in next section) through an elementary variable transformation,  $(x_i) = (e^{z_i})$ . Notice that the Elmore delay expressions provided in Equations (2.5) and 2.6 are a subset of the set of posynomials; specifically they are posynomials whose exponents belong to the set  $\{-1,0,1\}$ .

#### 2.5.2 Geometric programming

An optimization problem of the type,

minimize

$$f(\mathbf{x})$$

(2.10)

such that  $g_i(\mathbf{x}) \leq C, 1 \leq i \leq m$

$\mathbf{x} \in \mathbf{R}^+$

is a geometric programming problem if  $f(\mathbf{x})$  and  $g_i(\mathbf{x})$  are posynomials.

A geometric optimizer converts the above minimization problem, called the primal prob-

lem into a maximization problem called the dual problem. It uses the arithmetic-geometric inequality, which states that the weighted arithmetic mean of a set of positive numbers is at least as great as their geometric mean, to prove that the maximum of the dual problem is indeed the minimum of the primal problem.

The degree of difficulty of a geometric program is given as

degree = Number of terms

$$-$$

No. of variables  $-1$  (2.11)

When the degree of a geometric programming problem is zero, then the solution of the dual problem can be obtained by solving a system of linear equations. When the degree is greater than zero, the dual problem takes the form of a simple optimization problem, where all of the constraints are linear. Thus in either case, the dual problem is much simpler than the original or primal problem, and leads to fast solutions. A more in-depth treatment on geometric programming can be found in [13].

It can be noted that the area model mentioned in Section 2.1.1, is in the posynomial form. Moreover, if the Elmore model is used to evaluate the gate delay, then the path delay can be expressed as a summation of posynomials, and is hence a posynomial in itself. Thus the transistor sizing problem under these models is one of minimizing a posynomial function under posynomial constraints of the form mentioned in Equation (2.11), and is therefore a geometric programming problem.

# 2.6 Convex optimization

#### 2.6.1 Convex sets and convex functions

A set C in  $\mathbb{R}^n$  is said to be *convex* if, for every  $x_1, x_2 \in C$ , and every real number  $\alpha$ ,  $0 \leq \alpha \leq 1$ , the point  $\alpha x_1 + (1 - \alpha) x_2 \in C$ . This definition can be interpreted geometrically as stating that a set is convex, if given any two points in the set, every point on the line segment joining these two points is also a member of the set.

A function f defined on a convex set  $\omega$  is said to be convex if, for every  $x_1, x_2 \in \omega$ , and

every  $\alpha$ ,  $0 \le \alpha \le 1$ ,

$$f(\alpha x_1 + (1 - \alpha)x_2) \le \alpha f(x_1) + (1 - \alpha) f(x_2) \tag{2.12}$$

This can be geometrically interpreted as stating that a function is convex if the line joining any two points on it, lies above the function. A few results are listed below.

- (1) If f(x) is a convex function, the  $f(x) \leq c$  corresponds to a convex set.

- (2) The intersection of two convex sets is a convex set. However, the union of convex sets, in general, is not convex.

For further details on convexity, the reader is referred to [14]. Figure 2.2 shows examples of a convex set and a convex function.

Figure 2.2: Convex set and convex function

#### 2.6.2 Convex programming problem

A convex programming problem, also referred to as a convex optimization problem, involves the minimization of a convex function over a convex set. A problem of the type

minimize

$$f(\mathbf{x})$$

(2.13)

such that  $g_i(\mathbf{x}) \leq 0, 1 \leq i \leq m$

$\mathbf{x} \in \mathbf{R}^n$

is a convex programming problem if  $f(\mathbf{x})$  and  $g_i(\mathbf{x}), 1 \leq i \leq m$ , are convex functions.

The advantage of a convex programming formulation is that the problem is known to have the property that any local minimum is also a global minimum, and efficient optimization algorithms for solving such a problem are available. Therefore, it is desirable to attempt to express any optimization problem using a convex formulation, as far as possible, under the caveat that the accuracy of the modeling functions for the objective and the constraints must be preserved.

Section 2.5 showed that transistor sizing under the area and delay models from Sections 2.1 and 2.2 is a geometric programming problem. Under the variable transformation mentioned in Section 2.5.1 the transistor sizing problem takes the form of a problem of minimization of a convex function under convex constraints and hence is a convex programming problem. This indicates that under such models one can find a global optimum of the transistor sizing problem. Since the posynomial to convex function mapping mentioned in Section 2.5.1 is one-to-one, it can be used to claim that the minimum in original space corresponds to minimum in the transformed space.

In the next chapter a new delay gate model is proposed that retains the convexity property of the Elmore delay model.

# 2.7 Mixed integer nonlinear programs

A mixed integer nonlinear program (MINLP) is a nonlinear programming problem, where some of the variables  $x_i$ 's are required to have integer values. This problem is much more computationally expensive than continuous optimization problems. The reason is that in case of continuous optimization, gradient-based methods can be used to arrive at a minimum, either local or global. But in the case of MINLP, due to the presence of integer variables gradients are not available, since the function exists only at discrete points.

Obtaining computationally efficient heuristics that can provide reasonably good solutions to this problem is an area of active research. One typical approach involves creation of a branch-and-bound tree. Each node in the tree corresponds to a nonlinear program, and the

tree is bounded according to the solution of these nonlinear programs. One particular type of MINLP is the 0-1 integer nonlinear program, where the integer variables are constrained to have one of the two values. The application of the branch-and-bound method for this case results in a binary tree, where the left child of a node fixes its corresponding integer variable to 0, and the right child sets its to 1. This approach can result in reasonable computation times for smaller programs, but for general purpose optimizations involving thousands of variables and constraints, the approach is computationally prohibitive and unrealistic.

The second part of this thesis solves the  $V_t$  assignment problem, where two fixed levels of  $V_t$  are used. It will be shown later in Section 4.3 that this problem is in the MINLP form. Hence, Chapter 4 develops an efficient heuristic to solve this problem.

# Chapter 3

# Convex Delay Modeling

#### 3.1 Introduction

While building a timing optimization engine, it is essential for the underlying delay models to be accurate and efficient. Moreover, the task of obtaining globally optimal solutions is greatly eased if these models should possess convexity properties, as explained in Section 2.6. This chapter proposes an accurate circuit delay modeling procedure that results in provably convex delay functions.

The chapter is organized as follows. A brief summary of existing models is provided in Section 3.2. The idea of a generalized posynomial is presented in Section 3.3, and its application to gate delay modeling is discussed in Section 3.4. Section 3.5 presents the results demonstrating the accuracy of the new model, and a technique for converting generalized posynomial programs to posynomial programs is presented in Section 3.6. Section 3.7 presents a proof of convexity of path delays under this gate delay model and is followed by experimental results on circuit optimization in Section 3.7 that demonstrate the computational efficacy of the new model.

# 3.2 Existing delay modeling approaches

The Elmore delay model presented in Section 2.2 has been used traditionally to perform transistor-level delay analysis. This model, however, is known to be very inaccurate for

modern designs. This inaccuracy can be attributed to its failure to accurately consider important factors such as input transition times, the position of the switching transistor, the sizes of fighting complementary transistors, and the temporal relationship between inputs and transistor nonlinearities. As a result, exact optimization under this model may lead to an incorrect solution to the sizing problem since the timing model has a bad correlation with reality. More precisely, the solution may be either suboptimal in that it meets the timing specification without minimizing the cost function, or entirely inaccurate, in the sense that it may not meet the timing constraints at all. Therefore, it is immensely important to use more accurate timing models in sizing.

Several other approaches for accurate timing modeling have been proposed in the past. For example, one could model gate delays by developing closed form expressions [15]. Much work has been carried out in the development of closed form models for inverters and then mapping other gates to an equivalent inverter [16, 17]. An alternative approach uses a look-up table constructed using experimentally-derived delay data for various configurations, with intermediate data points being derived by interpolation methods, as in the delay model in [18]. However, this approach requires storage of large number of data points to guarantee accuracy and hence is very expensive in terms of memory requirements. Neither the closed-form modeling approach nor the table-look-up modeling method is particularly well suited for optimization since the modeling functions typically do not possess any convexity properties and cannot be used in the context of a formal optimization algorithm that is guaranteed to find the global minimum in a reasonable time. Moreover, it is not necessarily true that these models will have continuous derivatives, or, in the case of look-up tables, any derivative at all. Therefore, there is a need for new models that permit accurate delay computations, while maintaining convexity properties suited for optimization. This work derives a methodology for developing such models.

The theoretical underpinning of this approach is a result that defines a new class of functions that are shown to work well for modeling circuit delays. These functions are provably convex under a variable transformation that is explained in the next section. The set of functions from which these functions are chosen includes the set of posynomials as a proper subset, and therefore, we refer to these functions as *generalized posynomials*. This work uses a curve-fitting approach to find a least-squares fit from the delay function, computed by SPICE over a grid, to a generalized posynomial in order to provide guarantees on accuracy of the delay model.

## 3.3 Generalized posynomials

#### 3.3.1 Definitions

Posynomials and convex functions, described in Sections 2.5 and 2.6, are rich classes of functions and the basic motivation for this work is that better delay estimates can be obtained by fully exploiting this richness.

A generalized posynomial function  $G_k(\mathbf{x}), \mathbf{x} \in \mathbf{R}^n$ , where  $k \geq 0$  is called the order of the function, is defined recursively as follows:

1. A generalized posynomial of order 0,  $G_0$ , is the posynomial defined earlier:

$$G_0(\mathbf{x}) = \sum_{i} \gamma_j \prod_{i=1}^n x_i^{\alpha_{ij}}, \tag{3.1}$$

where the exponents  $\alpha_{ij} \in \mathbf{R}$  and the coefficients  $\gamma_j \in \mathbf{R}^+$ .

2. A generalized posynomial of order  $k \geq 1$  is defined as

$$G_k(\mathbf{x}) = \sum_j \gamma_j \prod_{i=1}^n \left[ G_{k-1,i}(\mathbf{x}) \right]^{\alpha_{ij}}, \qquad (3.2)$$

where the exponents  $\alpha_{ij} \in \mathbf{R}^+$  and the coefficients  $\gamma_j \in \mathbf{R}^+$ , and  $G_{k-1,i}(\mathbf{x})$  is a generalized posynomial of order k-1.

Specifically, the generalized posynomial of first order, is given by

$$f(\mathbf{x}) = \sum_{i} \gamma_i \prod_{j=1}^{m} \left( \sum_{l=1}^{p_i} \omega_{ijl} \prod_{s=1}^{n} x_s^{a_{ijls}} \right)^{\beta_{ij}}$$

(3.3)

where each  $\beta_{ij} \in \mathbf{R}^+$ , each  $a_{ijls} \in \mathbf{R}$ , each  $\gamma_i \in \mathbf{R}^+$ , and each  $\omega_{ijl} \in \mathbf{R}^+$ . Stripping Equation (3.3) of its complicated notation, one may observe that the term in the innermost bracket represents a posynomial function. Therefore, a generalized posynomial of first order is similar to a posynomial, except that the place of the  $x_i$  variables in Equation (2.9) is taken by a posynomial. Similarly, a generalized posynomial of order k uses a generalized posynomial of order k-1 in place of the  $x_i$  variables in Equation (2.9). Appendix A shows that if the range of interest of  $\mathbf{x}$  is restricted to the positive orthant where each  $x_i > 0$ , then under the variable transformation from the space  $\mathbf{x} \in \mathbf{R}^n$  to the space  $\mathbf{z} \in \mathbf{R}^n$  given by  $x_i = e^{z_i}$ , the generalized posynomial function f of Equation (3.2) is mapped to a convex function in the  $\mathbf{z}$  domain.

#### 3.3.2 Proof of convexity

convex function in the z domain.

**Theorem 1:** If the range of interest of  $\mathbf{x}$  is restricted to the positive orthant where each  $x_i > 0$ , then under the variable transformation from the space  $\mathbf{x} \in \mathbf{R}^n$  to the space  $\mathbf{z} \in \mathbf{R}^n$  given by  $x_i = e^{z_i}$ , the generalized posynomial function f of Equation (3.2) is mapped to a

The following theorem parallels the relationship between posynomials and convex functions.

**Proof**: It is well known that a generalized posynomial of order 0,  $G_0(\mathbf{x})$ , is transformed to a convex function,  $G_0(\mathbf{z})$  in the  $\mathbf{z}$  domain [19]. Since the functional form of the functions  $G_k(\mathbf{x}), k > 0$ , is different from that of  $G_0(\mathbf{x})$  due to the additional nonnegativity constraint on the  $\alpha_{ij}$  variables, they are treated separately.

The proof of Theorem 1 proceeds by considering  $G_k(\mathbf{z})$  for  $k \geq 1$ ; to prove its convexity, it is enough to prove the convexity of

$$L = P \prod_{i=1}^{m} (G_{k-1,i})^{\beta_i}, \beta_i \ge 0, \tag{3.4}$$

since a sum of convex functions is convex. The gradient and Hessian of this function are,

respectively, given by

$$\nabla L = P \sum_{i=1}^{m} \left\{ \left( \prod_{j=1, i \neq j}^{m} (G_{k-1,j})^{\beta_{j}} \right) \beta_{i} (G_{k-1,i})^{\beta_{i}-1} \nabla G_{k-1,i} \right\}$$

$$= L \sum_{i=1}^{m} \frac{\beta_{i} \nabla G_{k-1,i}}{G_{k-1,i}}$$

$$\nabla^{2}L = L \left\{ \left( \sum_{i=1}^{m} \frac{\beta_{i} \nabla G_{k-1,i}}{G_{k-1,i}} \right) \left( \sum_{i=1}^{m} \frac{\beta_{i} \nabla G_{k-1,i}^{T}}{G_{k-1,i}} \right) + \right.$$

$$\sum_{i=1}^{m} \frac{\beta_{i}}{G_{k-1,i}^{2}} \left( G_{k-1,i} \nabla^{2} G_{k-1,i} - \nabla G_{k-1,i} \nabla G_{k-1,i}^{T} \right) \right\}$$

(3.5)

We will prove that L is a convex function by showing that the matrix  $\nabla^2 L$  is positive semidefinite. Since the first term is easily seen to be positive semidefinite, the function L is convex if  $(G_{k-1,i} \nabla^2 G_{k-1,i} - \nabla G_{k-1,i} \nabla G_{k-1,i}^T)$  is positive semidefinite. We will now show this by proving the following result, by induction and the proof of Theorem 1 follows as an immediate consequence. The matrix  $(G_k \nabla^2 G_k - \nabla G_k \nabla G_k^T)$  is positive semidefinite for all  $k \geq 0$ .

Basis case Consider a zeroth order generalized posynomial given by

$$G_0 = \sum_{i=1}^p \omega_i \prod_{j=1}^n e^{a_{ij}z_j} = \sum_{i=1}^p h_i,$$

where  $h_i = \omega_i \prod_{j=1}^n e^{a_{ij}z_j}$ . It is easy to see that the value of each  $h_i$  is positive for all  $\mathbf{z}$ ; this observation is used later in the proof.

Now consider the matrix  $H = (G_0 \nabla^2 G_0 - \nabla G_0 \nabla G_0^T)$ . The  $(q, l)^{\text{th}}$  term of this matrix is given by

$$egin{array}{lll} H_{ql} & = & \left(\sum_{i=1}^{p}h_{i}

ight)\left(\sum_{i=1}^{p}h_{i}a_{iq}a_{il}

ight) - \left(\sum_{i=1}^{p}h_{i}a_{iq}

ight)\left(\sum_{i=1}^{p}h_{i}a_{il}

ight) \ & = & \sum_{i=1}^{p}\sum_{j=1,j

eq i}^{p}\left[h_{i}h_{j}\left(a_{iq}-a_{jq}

ight)\cdot a_{l}

ight] \ & = & \sum_{i=1}^{p}\sum_{j=i+1}^{p}\left[h_{i}h_{j}\left(a_{iq}-a_{jq}

ight)\cdot \left(a_{il}-a_{jl}

ight)

ight] \end{array}$$

Therefore, we can write

$$H = \sum_{i=1}^{p} \sum_{j=i+1}^{p} h_i h_j \left( ec{a}_i - ec{a}_j

ight) \cdot \left( ec{a}_i - ec{a}_j

ight)^T$$

where  $\vec{a}_i = [a_{i1}, a_{i2}, \cdots a_{in}]^T$ . Therefore, H is positive definite since each  $h_i > 0$ .

**Induction hypothesis**: For a generalized posynomial  $G_{k-1}(\mathbf{z})$  of order k-1, where  $k \geq 1$ ,

$$G_{k-1}(\mathbf{z}) \bigtriangledown^2 G_{k-1}(\mathbf{z}) - \bigtriangledown G_{k-1}(\mathbf{z}) \bigtriangledown G_{k-1}(\mathbf{z})^T$$

is positive semidefinite.

For the inductive step, we write

$$G_k = \sum_{i=1}^r L_{k,i} = \sum_{i=1}^k P_i \prod_{j=1}^{m_i} (G_{k-1,i,j})^{\beta_{i,j}},$$

(3.7)

so that each  $L_{k,l}$  is of the form of the function L defined in Equation (3.4). We may use the expressions for the gradient and Hessian of L in Equations (3.5) and (3.6) to write

$$G_{k} \bigtriangledown^{2} G_{k} - \bigtriangledown G_{k} \bigtriangledown G_{k}^{T}$$

$$= \left(\sum_{l=1}^{r} L_{k,l}\right) \left(\sum_{l=1}^{r} \bigtriangledown^{2} L_{k,l}\right) - \left(\sum_{l=1}^{r} \bigtriangledown L_{k,l}\right) \left(\sum_{l=1}^{r} \bigtriangledown L_{k,l}\right)^{T}$$

$$= \sum_{l=1}^{r} \sum_{q=1}^{r} \left(L_{k,l} \bigtriangledown^{2} L_{k,q} - \bigtriangledown L_{k,l} \bigtriangledown L_{k,q}^{T}\right)$$

If we set

$$\vec{u}_j = \sum_{j=1}^m \frac{\beta_j \nabla G_{k-1,i,j}}{G_{k-1,i,j}},$$

(3.8)

this may be rewritten as

$$\sum_{l=1}^{r} \sum_{q=1}^{r} L_{k,l} (L_{k,q} \{ \vec{u}_{q} \vec{u}_{q}^{T} + \sum_{i=1}^{m} \frac{\beta_{i}}{G_{k-1,q,i}^{2}} (G_{k-1,q,i} \bigtriangledown^{2} G_{k-1,q,i} - \bigtriangledown G_{k-1,q,i} \bigtriangledown G_{k-1,q,i}^{T}) \}) - L_{k,l} L_{k,q} \vec{u}_{l} \vec{u}_{q}^{T}$$

$$= \sum_{l=1}^{r} \sum_{q=1}^{r} L_{k,l} L_{k,q} \sum_{i=1}^{m} \frac{\beta_{i}}{G_{k-1,q,i}^{2}} (G_{k-1,q,i} \bigtriangledown^{2} G_{k-1,q,i} - \bigtriangledown G_{k-1,q,i}) + \sum_{l=1}^{r} \sum_{q=l+1}^{r} L_{k,l} L_{k,q} \sum_{i=1}^{m} (\vec{u}_{q} - \vec{u}_{l}) (\vec{u}_{q} - \vec{u}_{l})^{T},$$

which is positive semidefinite by the induction hypothesis. **QED**.

## 3.4 Delay modeling using generalized posynomials

Delay estimation is carried out by using precharacterization, which is performed once for every technology. For a given technology, the delay of a gate typically depends on the sizes of transistors in the gate, the input slope, and the output capacitance; and these are used as variables in the characterization procedure. These variables will be referred to as *characterization variables*. The choice of these circuit parameters as characterization variables can be better explained with the help of an example.

Let us consider the timing model for an inverter, such as the one shown in Figure 3.1; this model is generalized to complex gates in subsequent sections. The aim is to be able to estimate delay as a function of the pmos and nmos transistor widths,  $w_p$  and  $w_n$ , the input transition time  $\tau$ , and the output load capacitance,  $C_L$ . Therefore, for an inverter,  $w_p$ ,  $w_n$ ,  $\tau$ , and  $C_L$  form the set of characterization variables. These variables reflect the set of variables that are generally considered to be important in defining the delay of a gate in most models.

Figure 3.1: Inverter circuit

Several types of functions that are members of the generalized posynomial class, are tried out to achieve the desired levels of accuracy. The general form of expression that provided

consistently good results for different gate types is as follows

Delay =

$$\sum_{j=1}^{m} P_j \cdot \prod_{i=1}^{n} (x_i^{\Delta} + c_{ij})^{\beta_{ij}} + C$$

(3.9)

Here, the  $x_i$ 's are characterization variables, and the  $c_{ij}$ 's,  $\beta_{ij}$ 's, C, and  $P_j$ 's are real constants, referred to collectively as characterization constants. The parameter  $\Delta$  is set to either -1 or 1, depending on the variable, as will soon be explained. The problem of characterization is that of determining appropriate values for the characterization constants. It is shown in Section 3.7.1 that the use of this form of function implies that the circuit delay can be expressed as a generalized posynomial function of the transistor widths.

Due to the curve-fitting nature of the characterization procedure it is not possible to ascribe direct physical meanings to each of these terms. However, it can be seen that the fall delay increases as  $C_L$ ,  $w_p$  and  $\tau$  are increased, and decreases as  $w_n$  is increased, implying that an appropriate choice for the parameter  $\Delta$  for the first three variables is 1, and that for  $w_n$  is -1. Note that this is not as restrictive as the Elmore form since, among other things, the  $\beta_{ij}$ 's and  $c_{ij}$ 's provide an additional degree of freedom that was not available for the Elmore delay form. A similar argument may be made for the rise delay case.

A two-step methodology is adopted to complete the characterization. In the first step, a number of circuit simulations are performed, using HSPICE to generate points on a grid. In the second, a least-squares procedure is used to fit the data to a function of the type in Equation (3.9).

A series of simulations is performed to collect the experimental data using the HSPICE circuit simulator. The total number of data points, N, increases exponentially with the number of characterization variables. For the inverter circuit with four characterization variables and d data points for each variable to cover the range of interest, the total number of data points, N would be  $d^4$ . Therefore, it is important to choose the data points carefully; in particular, it is not necessary to choose an even grid for the transistor widths and a smaller granularity of points can be chosen for larger  $w_n$ 's in case of the fall transition.

The determination of the characterization constants was performed by solving the following nonlinear program that minimizes the sum of the squares of the percentage errors over all data points.

minimize

$$\sum_{i=0}^{N} \left[ \frac{D_{estim}(i) - D_{actual}(i)}{D_{actual}(i)} \right]^{2}$$

(3.10)

where N is the number of data points,  $D_{estim}(i)$  and  $D_{actual}(i)$ , respectively, represent the values given by Equation (3.9), and the corresponding measured value at the  $i^{th}$  data point. This minimization problem is solved using the MINOS optimization package [20] to determine the values of the characterization constants.

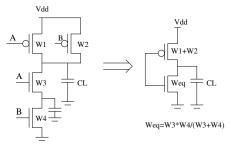

#### 3.4.1 Characterization of a set of primitives

For a library-based design, a full characterization of all cells is a viable alternative and its complexity is comparable to that of characterizing the library using any other means. For general full custom designs, however, the number of SPICE data points to be generated for the curve fit increases exponentially with the number of characterization variables. It is computationally expensive to perform such a large number of simulations and hence an alternative strategy is suggested. An alternative strategy is to precharacterize a set of logic structures such that any gate can be mapped to one of the elements of this set with some acceptable loss of accuracy. It is important to note that even under this procedure, the transistor sizing approach will size each transistor individually, and this method is only used for delay estimation.

One straightforward technique that may be used is to map all of the gates to an "equivalent inverter" [16, 17], and use the inverter characterization to estimate delays; the sizes of the pull-down nmos transistor and the pull-up pmos transistor of this inverter reflect the real pull-down or pull-up path in the gate. The widths of these new transistors are referred to as the equivalent widths. The equivalent width calculation is based on modeling the "on" transistors as conductances, and the equivalent width corresponds to the effective conductance of the original structure. Accordingly, if two transistors of widths  $w_1$  and  $w_2$

are connected in parallel, the equivalent width is defined as  $w_1 + w_2$  and if the transistors are connected in series, the equivalent width is defined as  $\left[w_1^{-1} + w_2^{-1}\right]^{-1}$ .

However, such a reduction has shortcomings. Consider the NAND gate in Figure 3.2(a), whose equivalent inverter approximation is illustrated in Figure 3.2(b). The node capacitances at nodes other than the output are not accounted for in this approximation. Also, the same mapping will be used irrespective of whether input A or B is switching, whereas in reality, these two cases correspond to different delay values. This issue is addressed in Section 3.4.1.

Figure 3.2: Inaccurate mapping of a NAND gate

The mapping procedure developed in this work attempts to reduce the errors caused because of such approximations. To this respect, a basic set of primitives is developed such that any arbitrary gate can be mapped to one of the primitives with acceptable loss of accuracy. Three types of primitives, namely, simple primitives, complex primitives and sequential primitives are developed to handle various logic structures, for both rise and fall transitions.

#### Simple primitives

One-input, two-input, and three-input primitives are developed as described below.

Single input primitive is basically an inverter; it is referred to as a primitive because of the fact that mapping procedure along with inverters also maps NOR gates for fall transition and NAND gates for rise transition on an inverter. For example, if we assume single input transitions, then in case of a NAND gate only one of the pmos transistors will be on during the rise output transition. The pmos transistor that is off contributes only as a loading

capacitance, and hence for rise delay calculation, the NAND gate is mapped to an inverter. Since this inverter primitive is identical to the inverter described in previous section it is not discussed any further.

It is necessary to emphasize that an n-input primitive does not mean that it is a primitive only for the n-input gates. Any gate having equal to or more than n inputs would be mapped to an n-input primitive depending upon the position of the switching transistor.

To illustrate this a set of two-input primitives for fall transition at the output is shown in Figure 3.3 (the presence of a load capacitance at the output is implicit and is not shown). We assume that the timing analysis procedure in our tool assumes only single input transitions, and hence there can only be one pair of pmos and nmos transistors switching at a time.

Figure 3.3: Two-input primitives for fall transition

A two-input NAND gate is shown in Figure 3.3(a). For the fall delay, if the input transition occurs at input A, then the gate is mapped to Figure 3.3(b). Note that since the output is being pulled down in the case of a fall delay calculation, the pull-down is retained while the pull-up is replaced by a single transistor, and the characterization equations of Figure 3.3(b) are used to estimate the delay. In a similar fashion, when the input transition occurs at input B of Figure 3.3(a), the gate is mapped to Figure 3.3(c). A similar procedure is applied for rise delays, i.e., the pull-up part is retained while the pull-down part is replaced by an equivalent nmos transistor. Similarly, 2-input primitives, containing two pmos transistors in series with an nmos transistor, namely PrimRiseA and PrimRiseB, are developed that can accurately model NOR gates and NOR gate-like structures.

For simple gates with more than two inputs and complex gates, an expanded set of

primitives is necessary. The set of primitives used to approximate such gates is shown in Figure 3.4. It should be noted that these are not the only primitives on which gates with more than three inputs will be mapped. For example, consider a three input NAND gate and the case where the latest arriving input is the one connected to the topmost transistor in the nmos chain. In this case, the NAND gate will be mapped to the two input primitive PrimFallA shown in Figure 3.3(a); the two nmos transistors at the bottom are collapsed into one transistor of equivalent width.

Figure 3.4: Three-input primitives

#### Complex primitives

One can see that above mentioned methodology can very efficiently handle various simple gates as well as complex gates under certain switching scenarios. However, for the gates with disjoints paths to power supply or ground, such as And-Or-Invert (AOI) gates, the methodology will not always give accurate delays. In case of simple gates with only one transistor chain, the internal node capacitances are inherently taken into account during the modeling phase. But in the case of AOI gates there are multiple parallel chains of transistors. Hence if AOI gates are mapped (except when all the transistors connected to the output and belonging to the nonconducting chains are off) on to the simple primitives developed earlier, then the internal node capacitances in non-conducting transistor chains would not be correctly accounted for, resulting in inaccurate delay values. When the internal node capacitances are charged then these capacitances need to be considered and hence a set of

complex (AOI) primitives is developed. The beauty of this approach is that these primitives can be developed as simple extensions of the primitives of simple gates. For AOI gates, one can observe that the worst case delay corresponds to one conducting chain of transistors between the output and supply, while all other chains are nonconducting. This shows that primitives for AOI gate can be developed by addition of a nonconducting transistor chain in parallel to the transistor chain in the simple gate primitive. A few example primitives for AOI gates are shown in the Figure 3.5.

Figure 3.5: Examples of AOI Primitives

For a general purpose arbitrary gate the longest resistive path is obtained to estimate worst case delay. In addition, the side inputs are assumed to have values that will maximize the loading capacitance. Then a systematic reduction to primitives can be obtained by using following rules:

- 1. If there is a chain of on transistors, then those transistors can be collapsed in an equivalent transistor without loss of much accuracy.

- 2. The position of switching transistor should decide the primitive to be used for delay evaluation. For example, if there are four nmos transistors in a chain with the topmost transistor switching and all of the remaining transistors on, then the chain can be collapsed to an equivalent transistor. On the other hand if any of the middle transistors is switching, then the transistors on the top can be collapsed in one equivalent transistor, and those at the bottom can be collapsed into another transistor, and the primitive with this structure can be used. The two cases will require different primitives because in the first case, all the on transistors act only as resistances, while in the latter case, the transistors on top have

both resistive and capacitive contributions, while those on the bottom exhibit only resistive effects.

- 3. If a chain of transistors does not include the switching transistor, then after collapsing into an equivalent transistor, one of the primitives developed for complex gates, for example the primitives showed in Figure 3.5, can be used.

- 4. If a chain of transistors is on, but one of the ends is floating then the internal capacitances are not charged, and the chain can be safely omitted from consideration, since it cannot have any effect on delay.

If the reduction results into an error above acceptable limits and if there are considerable number of instances of this gate, then it might justify investing efforts in fitting a model for that particular gate, and the fitting procedure mentioned in Section 3.4 can be used.

#### Sequential primitives

A static sequential element normally consists of a set of pass transistors and inverters. An example sequential element is shown in Figure 3.6. Since an inverter that drives a transmission gate forms a single channel connected component, as shown in Figure 3.6, a separate model is developed for this component. Using this model in conjunction with the inverter model explained earlier, we are now able to model every channel connected component in this sequential element. An advantage of the ability to develop accurate models for the sequential elements is the simplicity in constraint formulation in the across-latch optimization.

Figure 3.6: Sequential Element and Primitive

| Primitive                  | Delay   |           |  |

|----------------------------|---------|-----------|--|

|                            | Mean    | Deviation |  |

| InvRise                    | 0.31 %  | 2.84~%    |  |

| InvFall                    | 1.29 %  | 2.82~%    |  |

| PrimFallA                  | -1.28 % | 4.74 %    |  |

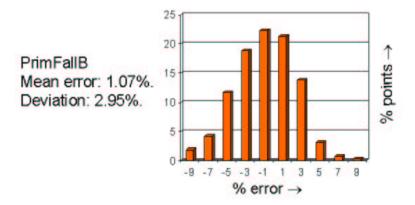

| PrimFallB                  | 1.07 %  | 2.95~%    |  |

| $\operatorname{PrimRiseA}$ | -0.67 % | 3.59 %    |  |

| PrimRiseB                  | 0.13 %  | 0.93 %    |  |

| PrimCoFall                 | -0.68 % | 2.96~%    |  |

| PrimCoRise                 | -0.35 % | 1.79 %    |  |

| AOI12Fall                  | 0.87 %  | 6.27~%    |  |

| SeqFall                    | 7.46 %  | 4.73 %    |  |

Table 3.1: Primitive Validation

### 3.5 Modeling Results

Table 3.1 shows the validation results of different primitives, proposed in Section 3.4.1, with respect to SPICE.

The purpose of listing these validation results on the primitives is to emphasize that transistor nonlinearities can be effectively modeled by convex functions and to test the validity of the basic idea of modeling delay as convex functions. Referring to Equation (3.9), a value of j=1 was chosen, and it was observed that the use of higher values for j did not offer significant improvements in accuracy. The characterization was performed in a 0.25 $\mu$ m technology by varying transistor widths to up to 80 $\mu$ m,  $\tau$  from 20 to 300 ps (10% to 90%) and  $C_L$  up to 800 fF. Figure 3.7 shows a typical histogram of the primitive validation.

Figure 3.7: Primitive validation

| Gate  | Delay                 |         |           |  |

|-------|-----------------------|---------|-----------|--|

|       | Output Transition     | Mean    | Deviation |  |

| Inv   | Rise                  | 0.31%   | 2.83 %    |  |

|       | Fall                  | 1.29~%  | 2.82~%    |  |

| Nor2  | Rise                  | 1.82 %  | 2.56~%    |  |

|       | $\operatorname{Fall}$ | 11.10~% | 5.06~%    |  |

| Nand2 | Rise                  | 5.18 %  | 6.17 %    |  |

|       | $\operatorname{Fall}$ | -0.46~% | 3.58~%    |  |

| Nor3  | Rise                  | 0.24 %  | 1.76~%    |  |

|       | Fall                  | 24.2~%  | 7.64~%    |  |

| Nand3 | Rise                  | 9.21~%  | 5.98~%    |  |

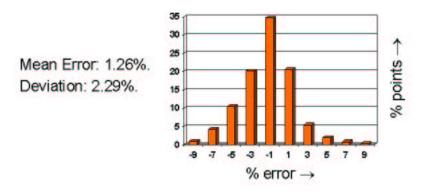

|       | $\operatorname{Fall}$ | 1.26~%  | 2.29~%    |  |

| AOI3  | Rise                  | 5.21 %  | 6.38~%    |  |

|       | $\operatorname{Fall}$ | 0.86~%  | 6.27~%    |  |

Table 3.2: Gate Validation

It should be noted that accurate fits are required only in the region where sizing constraints are satisfied. For example, if output transition time violates the specification then the optimizer will ensure that its value is reduced to a point in the feasible region, and the convexity of the functions will force the optimization to move to this region after some iterations.

Table 3.2 shows the validation results of various gates with respect to SPICE. It is important to note that that all the possible mappings for a gate are considered and the worst case results are shown in the table. For example, the fall transition on gate Nand3 can map on to either primitive PrimFallA, PrimFallB or PrimCoFall. It was found that PrimCoFall provided the best results, while PrimFallA and PrimFallB provided a smaller degree of accuracy due to the fact that a three input gate was mapped to a two-input primitive using the concept of an equivalent width of two series transistors. Figure 3.8 shows a typical histogram of gate validation.

The results show that the primitive-based gate delay estimation gives highly accurate results. It is observed that all of the errors that are above 2% are obtained when an n-input gate is mapped to a k-input primitive where k < n. If some gate type gives unacceptable results for some input transition we can further enhance the accuracy by characterizing the

Figure 3.8: Validation of a 2-input NAND gate

model for that specific scenario over a range of parameter values. It can be seen from the table that two of the delay scenarios, namely, fall delay of NOR2 and NOR3, resulted in an error greater than 10%, and that rise delay of NAND3 is close to 10% as well. The reason for these high errors is that an inverter primitive is used to estimate fall delay of a NOR gate and rise delay of a NAND gate. One rise primitive can be developed for NAND gate, and similarly for NOR gate to reduce the errors.