# **Informed Prefetching for Indirect Memory Accesses**

MUSTAFA CAVUS and RESIT SENDAG, University of Rhode Island, Kingston, RI JOSHUA J. YI, U.S. Courts, Western District of Texas, Waco, TX

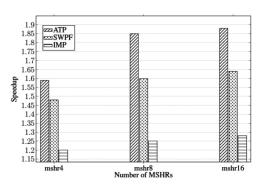

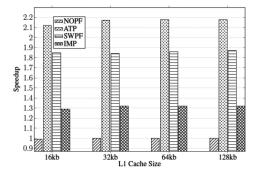

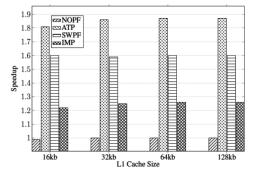

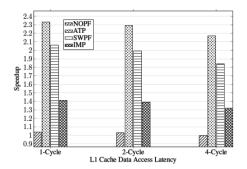

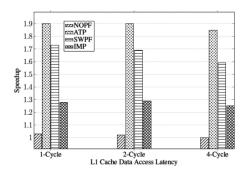

Indirect memory accesses have irregular access patterns that limit the performance of conventional software and hardware-based prefetchers. To address this problem, we propose the Array Tracking Prefetcher (ATP), which tracks array-based indirect memory accesses using a novel combination of software and hardware. ATP is first configured by special metadata instructions, which are inserted by programmer or compiler to pass data structure traversal knowledge. It then calculates and issues prefetches based on this information. ATP also employs a novel mechanism for dynamically adjusting prefetching distance to reduce early or late prefetches. ATP yields average speedup of 2.17 as compared to a single-core without prefetching. By contrast, the speedup for conventional software and hardware-based prefetching is 1.84 and 1.32, respectively. For four cores, the average speedup for ATP is 1.85, while the corresponding speedups for software and hardware-based prefetching are 1.60 and 1.25, respectively.

CCS Concepts: • Computer systems organization  $\rightarrow$  Architectures; • Software and its engineering  $\rightarrow$  Compilers; • General and reference  $\rightarrow$  Performance;

Additional Key Words and Phrases: Hardware and software prefetch, indirect memory access, computer architecture

### **ACM Reference format:**

Mustafa Cavus, Resit Sendag, and Joshua J. Yi. 2020. Informed Prefetching for Indirect Memory Accesses. *ACM Trans. Archit. Code Optim.* 17, 1, Article 4 (March 2020), 29 pages. https://doi.org/10.1145/3374216

#### 1 INTRODUCTION

Traversing sparse matrices and graphs frequently results in indirect memory accesses, which have irregular access patterns and thus poor cache spatial locality. These data structures are often implemented as nested arrays, e.g., A[B[i]], wherein the index of the outer array is the value stored in a memory location within the inner array. A hardware stream prefetcher can effectively prefetch entries of array B, because its entries are accessed sequentially, thus having good spatial locality. By contrast, because there may be no pattern to the values stored in array B, there is likewise no pattern in the accesses to array A, which diminishes the efficacy of a hardware stream prefetcher.

This article is an extended version of the following conference paper: Mustafa Cavus, Resit Sendag, and Joshua J. Yi, "Array Tracking Prefetcher for Indirect Accesses," IEEE International Conference on Computer Design (ICCD), Orlando, FL, USA, Oct 7–10, 2018. pp. 132–139.

This work was partly supported by NSF Grant No. 1422516.

Authors' addresses: M. Cavus and R. Sendag, Dept. of Elect., Comp. and Biomed. Eng., Univ. of Rhode Island, Kingston, RI 02881, USA; emails: {mcavus, sendag}@uri.edu; J. J. Yi, U.S. Courts, Western District of Texas, Waco, TX 76701; email: joshua\_yi@txwd.uscourts.gov.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

1544-3566/2020/03-ART4

https://doi.org/10.1145/3374216

4:2 M. Cavus et al.

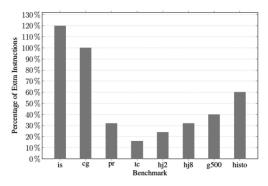

Fig. 1. Instruction overhead of software prefetching as a percentage of the instructions in the main loop.

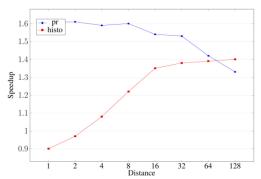

Fig. 2. Effect of prefetch distance on software prefetching speedup.

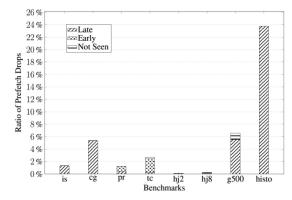

Software prefetching can hide the memory latencies of indirect memory accesses but requires executing additional instructions (e.g., the prefetching instructions themselves, instructions for address calculation and border checking, etc.). See, e.g., Reference [1] (describing a compiler-based system to generate software prefetches for indirect memory accesses). Figure 1 shows the percentage increase in the number of instructions in a loop iteration due to software prefetching for various benchmarks. For some benchmarks, e.g., *Integer Sort* (*is*), and *Conjugate Gradient* (*cg*), the overhead is very high (e.g., approximately 100%) as those benchmarks have relatively few instructions in each iteration. *Graph500* (*g500*) has a high instruction overhead due to border checking instructions in the frequently executed loop. While the benefit of prefetching may offset the overhead for some benchmarks (e.g., *is* and *g500*), for others (e.g., *cg*), the reverse is true.

In addition to instruction overhead, the benefit of software prefetching is further limited by (1) dependences related to prefetch address calculation, which may reduce the prefetch distance (i.e., how far (in terms of number of iterations) in advance of the memory access the prefetch instruction is issued), and (2) the lack of run-time information, which is required to optimally place the prefetch instructions. Figure 2 depicts the effect of prefetch distance on speedup for two benchmarks, Histogram (histo) and PageRank (pr). For histo, the highest speedup occurs at the largest prefetch distance (128) while the speedup is lower for smaller distances, especially for prefetch distances of 1, 2, 4, and 8. The opposite is true for pr, namely, the highest speedups occur at the smallest prefetch distances. histo has an indirect memory access behavior of the form A[B[i]] and as shown by Ainsworth and Jones [1], larger distance values (e.g., 32 or 64) are more effective for simple two-level indirect accesses. For pr's A[B[i][j]] structure, because the second dimension of array B, i.e., j, is short (16 for the inputs we used), prefetch addresses are calculated based on the first dimension instead. This increases the number of instructions executed between two consecutive accesses to the first dimension of array B, which suggests using shorter distances. For a set of memory-bound benchmarks with indirect memory accesses, the prefetch distance has a very significant effect on the speedup of software prefetching. More specifically, the average speedup across all benchmarks ranges from 1.19 (worst) to 1.84 (best). Finally, it is also important to remember that the optimal prefetch distance for a given application may change based on running the application on a different underlying architecture [1], which further underscores the necessity of run-time information to optimally place the prefetch instructions.

Hardware prefetchers, by contrast, do not require core pipeline executing additional instructions to compute and issue prefetches. But, to capture irregular access patterns, hardware prefetchers generally require very complex mechanisms. See, e.g., Hashemi et al. [2] (describing continuous

runahead execution). Yu et al. [3] proposed a pure hardware mechanism called Indirect Memory Prefetcher (IMP), which was designed to capture a few different indirect memory access patterns (e.g., A[B[i]] and A[B[C[i]]]).

Code Snippets 1(a)–1(c) below illustrate the limitations of hardware prefetching and concomitantly the advantages of software prefetching. We use IMP as an exemplary hardware prefetcher given its efficacy and relatively low complexity. Code Snippet 1(a) depicts an indirect memory access where the index array, i.e., B, is a multidimensional array. This type of code appears in benchmarks such as *PageRank (PR)* and *Triangle Count (TC)*. A hardware prefetcher like IMP can capture this indirect memory access by prefetching A[B[i][j+D]], where D is the prefetch distance. Even when the maximum number of iterations for the inner loop is very small, IMP can still capture these indirect memory accesses, but it may not be able to fully hide the memory latency as the prefetch distance is too small. But, in this case, increasing the distance actually decreases performance, because inner loop is too short. Software prefetchers solve this problem by prefetching memory accesses for the next iteration in the outer loop, e.g., A[B[i+4][j]]; hardware prefetchers, however, have trouble detecting this behavior.

Code Snippets 1: (a) Two-dimensional array in a nested loop. (b) Index requires arithmetic/logical computations. (c) Code requires simultaneous tracking of multiple indirect accesses of varying depth using the same index array.

Code Snippet 1(b) depicts an indirect memory access that requires arithmetic/logical operations to compute the memory address. More specifically, the index to array A requires a logical AND and a right-shift. This type of code appears in benchmarks such as *HashJoin ph2* (*hj2*). Most hardware prefetchers such as IMP cannot capture these memory accesses, because they require more than one arithmetic/logical operations; expensive hardware prefetchers, e.g., continuous runahead execution [2], can successfully prefetch this type of indirect memory access but only when runahead is sufficiently far and dependence chain can be successfully detected.

Code Snippet 1(c) depicts an example of when multiple indirect accesses of varying depth appear at the same time. In this situation, because tracking these memory accesses in hardware is very complicated, IMP does not capture the full behavior. More specifically, IMP was able to detect and prefetch B[C[i]] and D[C[i]], but not A[B[C[i]]]. IMP can track A[B[C[i]]], but only if it does not exist at the same time as D[C[i]].

By contrast, software prefetching can accurately prefetch the memory accesses depicted in the above code snippets, but only with substantial programmer effort. Also, prefetching these memory accesses requires significant overhead, because it requires performing the arithmetic/logical operations for every prefetch. Last, the best prefetching distance is hard to predict due to lack of run-time information.

Given that software and hardware prefetchers have different strengths and weaknesses, in this article, we propose a prefetch mechanism that attempts to combine the strengths of each. More specifically, we propose the Array Tracking Prefetcher (ATP), which tracks array-based indirect memory accesses such as A[B[i]], A[B[c[i]]], A[B[i][j]], and A[func(B[i])], where func() comprises some arithmetic and binary operations, and combinations of these array-based indirect memory access types. Rather than using software to insert prefetching instructions, ATP uses special metadata instructions to pass data structure traversal information to the hardware

4:4 M. Cavus et al.

component. These metadata instructions execute outside of the loop, so they do not result in significant instruction overhead. ATP's hardware component uses the data structure traversal information to configure itself, based on the behavior of the software that can significantly reduce the training time. Furthermore, by passing this traversal information, ATP's hardware component does not need to detect the indirect memory access behavior itself, which simplifies the complexity of the hardware while still enabling it to prefetch a wide variety of indirect memory accesses.

Concurrent with our work, Ainsworth and Jones [51] proposed a more general system with programmable RISC cores to implement an event-triggered prefetcher (ETP). While this method would perform well for capturing complex indirect access patterns, it does this with higher hardware cost, more complex programming interface and relatively expensive operations per event. ATP is custom hardware that can be configured with sufficient programmability for a variety of access patterns It is configured once as opposed to each time a trigger event is observed. In terms of prefetching indirect access chains, ATP and ETP are quite different. While ETP uses an event-triggered methodology, ATP uses pipelined prefetch model. In our early evaluations of ATP, we abandoned the event-triggered model, because pipelined prefetch model achieved better performance on our workloads.

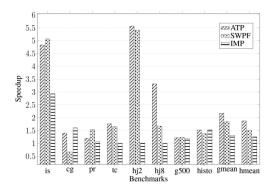

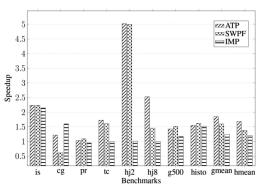

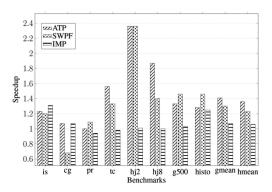

Across a set of memory-bound benchmarks, for a single-core architecture, ATP achieved an average speedup of 2.17× (with a maximum of 5.57×) over the no prefetching baseline. By comparison, software prefetching (using manually inserted and hand-tuned prefetching instruction) had an average speedup of 1.84× while a state-of-the-art indirect hardware prefetcher (IMP) had an average speedup of 1.32× only. For a four-core architecture, ATP had an average speedup of 1.85× (up to 5.02×) while software prefetching and IMP had average speedups of 1.60× and 1.25×, respectively.

# 2 ARRAY TRACKING PREFETCHER (ATP)

ATP is an integrated software/hardware approach to prefetching indirect data access patterns. The remainder of this section describes the software and hardware components in more depth.

### 2.1 ATP's Software Component

The software component of the ATP extracts information related to indirect memory accesses within a loop and passes this information to the hardware component. The programmer can manually mark this loop as shown in the Code Snippet 2(a) or can use the compiler to automatically identify the loop using an approach that is similar to that described in Reference [1]. The software component passes this extracted indirect-access information to the hardware component through special metadata instructions called *Array Tracking Instructions* (*ATIs*), as shown in Code Snippet 2(c).

2.1.1 Array Tracking Instructions (ATIs). Each ATI is a single 6-byte long instruction (two bytes for the opcode, 2-bits to specify the type of the ATI instruction, and the remainder for the operands). When a core detects an ATI instruction, the core removes it from the pipeline and forwards it to the ATP hardware. Because ATI instructions appear only once for each main loop where indirect access traversals occur, the number of executed ATI instructions is insignificant.

There are four types of ATIs: ATCL, ATAR, ATRL, and ATOP. ATCL clears all ATP tables. It does not have any operands. ATAR inserts entries into the ATP's Array Table (AT). It has a single operand, a 16-bit offset (from ATAR's PC), which is used to compute the PC of the load instruction that accesses the index or target array involved in indirect accesses.

| Basic (1D index array)                   | Pointer (2D index)                                                            | Multi-level | Multi-way (more<br>than one indirect<br>structure)                                                       | Hashed index                                                               |

|------------------------------------------|-------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| A[B[i]]                                  | A[B[i][j]]                                                                    | A[B[C[i]]]  | A[B[C[i]]] and<br>A[D[j]]                                                                                | A[(B[i]-1) & 0xf]                                                          |

| atar pcA<br>atar pcB<br>atrl pcB, pcA, 0 | atar pcA<br>atar pcB1<br>atar pcB2<br>atrl pcB2, pcA, 0<br>atrl pcB1, pcB2, 1 |             | atar pcA<br>atar pcB<br>atar pcC<br>atar pcD<br>atrl pcB, pcA, 0<br>atrl pcC, pcB, 0<br>atrl pcD, pcA, 0 | atar pcA<br>atar pcB<br>atrl pcB, pcA, 0<br>atop fsub, 1<br>atop fand, 0xf |

Table 1. Example Sequences of ATI Instructions for Different Types of Indirect Array Traversals

```

#at_indacc_loop

for (i = 0; i < N; i++)

sum += A[B[i]];

(a)

4005a0:

movslq

(%rax), %rcx

; load B[i]

4005a3:

add $0x4, %rax

4005a7:

add

(%rsp, %rcx, 4), %edx

; load A[B[i]]

%rsi, %rax

4005aa:

cmp

4005ad:

jne

(b)

clear AT tables

atcl

atar $0x4005a0

; Pass PC of the load for array B

atar $0x4005a7

; Pass PC of the load for array A

Pass the relationship between B and A

$0x4005a0,

$0x4005a7.

```

Code Snippets 2: Finding indirect accesses in software. (a) Marking the loop for indirect prefetching. Note that the compiler can automatically perform the marking and generate ATI instructions using a pass similar to approach in Reference [1]. (b) Instructions inside the marked loop. (c) ATI instructions generated (these instructions are placed above the entry point of the loop).

The ATRL instruction inserts relationship information between two arrays into the Indirect Relation Table (IRT), which is described in more detail in Section 2. For example, for the A[B[i]] structure, the software mechanism uses an ATRL instruction to insert an entry into the IRT to account for the relationship between target array A and index array B. ATRL has three operands: the first two are the PCs (offsets) of the load instructions accessing the index and target arrays, while the third operand (1-bit) specifies the type of the relation: 0 is used for A[B[i]] type accesses while 1 is used for A[B[i][j]] type accesses.

The ATOP instruction is used to calculate the index of the target array, e.g., func(B[i]), in complex data structures, e.g., A[func(B[i])]. More specifically, ATOP inserts these operations to ATP's Operation Table (OT). ATOP has two operands. The first operand specifies the operation type (e.g., NOT, ADD, etc.) while the second specifies the data for that operation. If there is more than one operation, then the software mechanism uses multiple ATOP instructions, one for each operation. The first operand of the first ATOP instruction is implicitly specified as the index array value (e.g., B[i]). The second ATOP uses the result of first ATOP as its first operand. The first ATOP instruction always follows an ATRL instruction. Table 1 shows example sequences of ATI Instructions for different types of indirect array traversals targeted in this article. ATP can simultaneously keep track of multiple indirect array access structures with various levels of complexity.

4:6 M. Cavus et al.

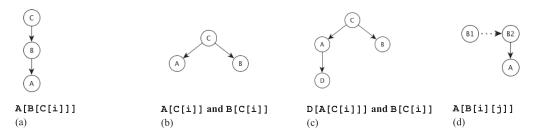

Fig. 3. Dependency graph generated from the Code Snippets 2(b).

2.1.2 Generating ATIs. Generating ATIs consists of two stages. First, the software component generates a dependency graph of the instructions inside a marked loop. Figure 3 depicts the dependency graph for the code loop shown in Code Snippet 2(b) (PC 4005a0 refers to accesses to array B and PC 4005a7 refers to accesses to array A in Code Snippet 2(b). Second, the software component generates ATIs based on the type of node or its connections. More specifically, for nodes that correspond to a load instruction, the software component generates an ATAR instruction. The software component generates ATRL instructions (e.g., when one load instruction is used to calculate the address of another load instruction) and ATOP instructions (if the index for the outer array requires computation) based on the connections of the nodes. The software component places these instructions above the entry point of the loop. The software component also places ATCL instructions before the beginning of the loop to clear the ATP tables before the loop begins to execute.

ATIs are often inserted on top of the outermost loop when there are multiple nested loops. If ATIs are inserted above the entry point of the inner loop, then the outer loop will be ignored by ATP. In this case, ATP will be initialized each time the inner loop is entered. This is often not desirable and it is only beneficial if the inner loop iterates sufficiently long so that ATP can calculate prefetches for future iterations of the loop.

# 2.2 ATP's Hardware Mechanism

The hardware mechanism is the part of the ATP that actually prefetches the indirect accesses. More specifically, the hardware mechanism of the ATP uses the information provided by ATIs to initialize the ATP tables. During execution of the loop, the ATP calculates the prefetching stride based on the base address of the required arrays, e.g., the address of A[0]for A[B[i]] indirect access, and the size of the array type. The hardware mechanism generates prefetch addresses for forthcoming indirect memory addresses based on the base address and predicted stride. The ATP also includes a mechanism to dynamically change the prefetch distance to adapt to specific runtime behavior to achieve better timeliness and performance.

2.2.1 High-level Description of the Operation of ATP's Hardware Mechanism. Due to the potential complexity of the hardware mechanism, before diving into the detailed description, it may be useful to first explain the operation of the hardware mechanism from a 30,000 foot view.

The hardware mechanism initiates the prefetch process after the load instruction commits. More specifically, when a load commits, the hardware mechanism checks whether that load instruction corresponds to an index array (by checking if the PC of that load instruction was previously inserted into the array table (AT) via an ATAR instruction). If that load instruction does not correspond to an index array, then the hardware mechanism takes no action. But if the load instruction corresponds to an index array, then the hardware mechanism will (eventually) issue prefetches based on the type of indirect access and a (dynamically varying) distance (in terms of the number of iterations). For example, for an A[B[i]] type of indirect access, when the load instruction corresponding to B[i] commits, the hardware mechanism checks whether B[i] is an index array. Because it is in this case, the hardware mechanism will issue prefetches for the future accesses to A[B[i]] and B[i]. In particular, for an A[B[i]] type of indirect access, the hardware mechanism

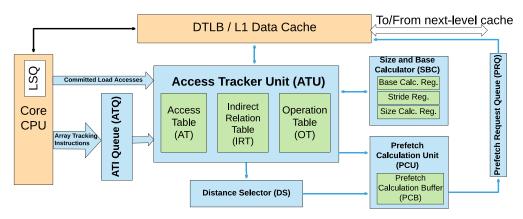

Fig. 4. An overview of ATP.

will issue prefetches for B[i+2\*distance] and A[B[i+1\*distance]]. Because there is a read-after-write dependence between array A and array B (i.e., the value at B[i] is used as the index for array A), the prefetch for array B needs to be for an iteration further into the future than the iteration being prefetched for array A.

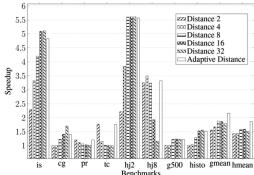

The hardware mechanism dynamically chooses the distance value by testing various distances (2, 4, 8, and 16 in our simulations) and then choosing the value with the best performance. (The hardware mechanism periodically reevaluates what the best distance is.) Assuming that the best distance is 16, then for an A[B[i]] type of indirect access, the hardware mechanism will issue prefetches for 32 iterations into the future for B[i] (i.e., B[i+2\*16]) and 16 iterations into the future for A[i] (i.e., A[B[i+1\*16]]).

If the indirect access is of the form A[B[C[i]]], then when the load instruction corresponding to C[i] (which is the index array in this case) commits, the hardware mechanism will issue prefetches for C[i+3\*distance], B[C[i+2\*distance]], and A[B[C[i+1\*distance]]].

If the indirect access is of the form A[B[i][j]] (where B[i] is a pointer to B[i][0]), then the prefetch calculation is triggered by the committed load instructions corresponding to either B[i] or B[i][j]. When the load instruction corresponding to B[i] commits, the hardware mechanism will issue prefetches for B[i+3\*distance]. When the load instruction corresponding to B[i][j] commits, the hardware mechanism will issue prefetches for B[i+2\*distance][j] and A[B[i+1\*distance][j]]. It is important to note that, we need to access B[i] to be able to calculate the address of B[i][j]. The prefetch for B[i] needs to be issued for an iteration further into the future than B[i][j] so the prefetched value of B[i] is available when it is needed.

Finally, if the indirect access is of the form A[func(B[i])], then when the load instruction corresponding to B[i] (which is the index array in this case) commits, the hardware mechanism will issue prefetches for B[i+2\*distance] and A[func(B[i+1\*distance])]. For this indirect structure, the value of B[i] is often used as an input to one or multiple arithmetic/binary operations, and hardware mechanism should perform these calculations to be able to calculate the prefetch address of A[func(B[i])].

2.2.2 Detailed Description of the Components (and Operation Thereof) of the Hardware Mechanism. Figure 4 depicts the block diagram of the hardware mechanism. It consists of an ATI queue (ATQ), an Access Tracker Unit (ATU), a Size and Base Calculator (SBC), a Prefetch Calculation Unit (PCU), and a Distance Selector (DS). After an ATI instruction has been identified in the processor pipeline, it is forwarded to the ATQ, which is a FIFO queue with head and tail pointers. A

4:8 M. Cavus et al.

|       |         |          |           |             | Ar           | ray Table (. | AT)  |              |       |          |           |           |

|-------|---------|----------|-----------|-------------|--------------|--------------|------|--------------|-------|----------|-----------|-----------|

| valid | load_pc | base_bit | base_addr | trigger_bit | trigger_type | size_bit     | size | indirect_map | depth | root_bit | root_addr | root_size |

| 1     | PC_A    | 1        | Base A    | 0           |              | 1            | 8    | 00           | 1     | 0        |           |           |

| 1     | PC_B    | 0        |           | 1           | 1            | 1            | 4    | 10           | 2     | 0        |           |           |

| 0     |         |          |           |             |              |              |      |              |       |          |           |           |

| 0     |         |          |           |             |              |              |      |              |       |          |           |           |

|       | Indirect F  | Relation T | able (IRT) |        |

|-------|-------------|------------|------------|--------|

| valid | destination | type       | op_bit     | op_idx |

| 1     | 0           | REG        | 1          | 0      |

| 0     |             |            |            |        |

|       | (   | peration | Table (OT) |          |

|-------|-----|----------|------------|----------|

| valid | op  | data     | next_bit   | next_idx |

| 1     | AND | 0X7f     | 1          | 1        |

| 1     | MUL | 14       | 0          |          |

| ATI Instructions |               |  |  |  |

|------------------|---------------|--|--|--|

| atar             | PC_A          |  |  |  |

| atar             | PC_B          |  |  |  |

| atrl             | PC_A, PC_B, 0 |  |  |  |

| atop             | fAND, 0x7f    |  |  |  |

| atop             | fMUL, 0xe     |  |  |  |

Fig. 5. The final state of the AT, IRT, and OT when they are initialized for a  $A[(B[i]\&0\times7f)*14]$  structure. A is an array of 8-byte doubles and B is an array of 4-byte integers.

sub-opcode field identifies individual ATI instructions. The ATQ is simply the interface between the processor pipeline and the ATP. ATP's prefetch generation consists of four stages: (A) First, ATIs in the ATQ are processed and used to initialize the ATU tables. (B) Once all ATIs have been processed, SBC starts calculating the sizes and base addresses for index and target arrays, which is needed for prefetch calculation. (C) Then, whenever the ATU observes a demand access to an index array, it notifies the PCU to begin the prefetch calculation process and issue prefetches (index array is also called trigger array, since prefetch calculations are triggered by accesses to this array). (D) Finally, the prefetch distance is dynamically adjusted based on the feedback from the DS, which finds the best performing prefetch distance using a simple mechanism. The overall process flow is managed by a finite-state machine (FSM). Next, we explain the operation of ATP in these four stages.

# A. Processing of ATI instructions and ATP initialization

Each valid ATI in the ATQ is processed in-order from ATQ's head to tail. ATIs are used to initialize/program the ATU tables. The ATU consists of three important tables, the Array Table (AT), the Indirect Relation Table (IRT) and the Operation Table (OT). An ATCL instruction resets all the ATU tables, namely valid bits are set to zero in the AT, IRT and OT. We explain how ATI instructions initialize or program ATU tables using the example in Figure 5, which shows the final status of the AT, IRT, and OT after they are initialized for A[(B[i]&0×7F)\*14] structure. The indirect access structure in this example generates two ATAR instructions, one for array A and one for array B. The ATAR instructions updates the AT. Each ATAR instruction reserves the next available entry in the AT. It specifies a load PC that is involved in reading an array element (and involved in indirect access). The fields in the AT are shown in Figure 5. Detailed description of each field in the ATU tables is given in Table 2. Initially, trigger-bit and depth field of the AT is 1. Trigger type, indirect map, and root fields are all initially 0s.

For the example in Figure 5, following the two ATAR instructions is an ATRL instruction specifying the relation between arrays A and B. Each of the PCs specified by ATRL have already been placed in the AT due to prior ATAR instructions. When an ATRL instruction is executed, it allocates an entry in the IRT, locates the index array's PC (B) in the AT and updates the indirect map field of the AT entry with the index of the IRT entry it allocated. Then, it locates the target array PC (A) in the AT and saves its index in the destination field in the IRT entry. Indirect map field of the AT is a bitmap (each bit refers to an index of IRT entry) specifying if an IRT entry in relation to the array in the current AT entry exists. 00 means no relation exists and thus array in that AT entry is not used as an index for any target array. In Figure 5, AT's entry 1 for array B has a non-zero indirect map, 10, suggesting the 0th entry in the IRT table provides in its destination field a pointer to the target array (in the AT) for which array B is used as index for. If all indirect maps are 0, then ATP acts as a stream prefetcher. This will happen when no ATRL instruction is observed for ATAR instructions.

Table 2. Detailed Explanation of the Fields in the AT, IRT, and OT

| Field Name          | Detailed Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AT/IRT/OT.valid     | Specifies if the entry is valid or not. Initial value is zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AT.pc               | The PC of the load instruction that accesses an array element involved in indirect access. This could either be index or target array access PCs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AT.base_bit         | Set when (and if) base address calculation has been completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AT.base_addr        | Start (base) address of an indirectly accessed array. For example, for A[B[i]] structure, base address is needed for array A (address of A[0]).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AT.trigger_bit      | Set if array in this entry is a trigger array. A trigger array must be an index array where its value is used as index to a target array. For multi-level structures, the trigger array is the highest depth (inner most) array.                                                                                                                                                                                                                                                                                                                                                                                   |

| AT.trigger_type     | Two types of trigger accesses are recognized by ATP: regular (type 0) and pointer (type 1). Regular refers to a direct access as in A[B[i]]. Pointer triggers refer to two-dimensional index array structures, such as A[B[i][j]].                                                                                                                                                                                                                                                                                                                                                                                 |

| AT.size_bit         | Set when size calculation has been completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AT.size             | Size (in bytes) of the array element. This information can be supplied by software. It is, however, easy to compute it at-run-time also.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AT.indirect_map     | A bitmap, where each bit refers to a specific IRT entry holding the array's indirect relation to its target array. If multiple bits are set in the bitmap, then this array is used as index for more than one target array.                                                                                                                                                                                                                                                                                                                                                                                        |

| AT.depth            | Level of an indirect access. A[B[i]] is a two-level indirect access (depth of A and B are 1 and 2, respectively), whereas A[B[C[i]]] is a three-level indirect access (depth of A, B, and C are 1, 2, and 3, respectively). Depth is used for indirect prefetch calculation.                                                                                                                                                                                                                                                                                                                                       |

| AT.root_bit         | Set when root address has been calculated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AT.root_addr        | Used only for trigger type 1 entries. Updated dynamically during prefetch calculation when necessary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AT.root_size        | Size (in bytes) of the root array element size.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AT.node_bit         | Set when (and if) it is an access to the first node of a linked list.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AT.node_offset      | Offset value from the current node address to the next node's pointer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AT.num_nodes        | Number of expected nodes in each linked list.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| IRT.destination_idx | The index of the AT entry that holds the target array for this base (index) array. For A[B[i]], destination idx is the index of the AT that holds array A.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IRT.type            | Specifies the indirect relation type. Two types are supported: direct and pointer. In direct relation, the value read from the base (index) array is used as an index or used in calculation of the index for the target array. Code Snippet 1 demonstrates a direct type. Pointer types are used to connect type 0 trigger entries of base arrays to type 1 trigger entries of destination arrays. In pointer type, value read from the base array is used as the root address of destination access. Root addresses are used to calculate prefetch addresses for incoming dimensions in a two-dimensional array. |

| IRT.op_bit          | Set if operations need to be performed on index array for target array index calculation (See Figure 5 as example).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IRT.op_idx          | The index of the OT entry that specifies the operation to perform.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OT.op               | Operation to perform on index array values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OT.data             | Data needed for operation. The first operand is the index array value if previous entry's next_bit is zero. Otherwise, the first operand is the result of the previous operation.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| OT.next_bit         | Set if another operation (specified in the next OT entry) needs to be performed after the current operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

4:10 M. Cavus et al.

Level (or depth) of an indirect access depends on the number of indirect accesses made in a chain starting with the access to the index array. AT has a field, depth, monitoring this level. ATRL updates the depth field of the base array (B) by checking if it is less than the depth of the target array, A. If so, then it sets the depth of array B to be one more than its target array (in this example, 2). The index array has the highest depth and a target array that is not an index to another target array has the lowest depth, 1. Depth is used for prefetch address calculation as described in Section 2C.

Finally, ATRL is followed by ATOP instructions, since base array is not directly used as index for the target array. The first ATOP is an AND with data 0×7f and the second ATOP is a MUL with 14 as its data. ATOP instructions can only follow an ATRL or another ATOP instruction. ATOP sets to 1 the op bit of the IRT entry it corresponds to denoting that base array must undergo an operation before used as index for target array. op\_idx field specifies the index of the OT that corresponds to the operation specified by ATOP. If ATOP is followed by another ATOP, then the next bit field of the last ATOP is set to 1. Once the last ATOP in the ATQ have been processed, ATU has completed initialization and ATP is ready to move to the size and base calculation stage.

### **B. Size and Base Address Calculation**

Before prefetching can start for indirect accesses, the stride of the trigger arrays and, the element sizes and base addresses of the target arrays must be known. ATP employs a single mechanism to compute sizes and base addresses.

**Size Calculation:** For each committed load instruction (to make sure that accesses are monitored in-order), if its PC is found in the AT table, and if the size bit is zero, ATP's Size and Base Calculator (SBC) starts the process for size computation. First, the stride between two accesses of the trigger array is computed. The SBC uses a stride register to keep track of trigger array accesses. A stride register consists of a valid bit, an index to the AT (holding the trigger array), last address, stride, and confidence fields. If the observed stride (difference between addresses of two consecutive accesses) repeats, then confidence counter is incremented. If confidence reaches a certain threshold, then the detected stride is saved in the AT entry corresponding to the trigger array and its size bit is set. The stride register is then released to be used by other trigger arrays.

The size calculation for a non-trigger array uses a different method. If the size bit is not set for a non-trigger array in the AT, then SBC employs a size calculation register (SCR) for that AT entry, which monitors the values read by index arrays and the resulting addresses of the non-trigger array. SCR consists of a valid bit, two AT index fields, two address fields, two computed index (idx) fields, confidence and size fields. SCR holds the AT index or indexes that hold the index array/s for the target array (the non-trigger array). For each committed load, if the index arrays were accessed, then the values read from these arrays are recorded in the computed index field (idx) of the SCR, and if the OT has any entry for the relation related to that index array, then the operation/s are performed on these values to compute the final index (idx1) for the target array and computed index field of SCR is updated. When an access to the non-trigger array is observed (after access to its index array), its address (addr1) is recorded in the SCR. Once SCR observes two addresses (addr1 and addr2) and two indexes (idx1 and idx2), the size of non-trigger array is computed using Equation (1). The size computation is repeated multiple times until a certain confidence threshold is reached. After size is computed, its recorded in the AT entry corresponding to the non-trigger array, and SCR is released:

$$Size (A) = \frac{Addr (A [B [i + 1]) - Addr (A [B [i]]))}{B [i + 1] - B [i]}.$$

(1)

**Base Address Calculation:** Finally, before indirect prefetching can be performed for target arrays, their base addresses must be computed. SBC assigns a base address calculation register (BACR) to a non-trigger type entry of a destination array if the base address of it is not yet

calculated but the size of it is already known. The value of the idx field in the BACR is set to the index of the AT entry that it is assigned for. Like the SCR, BACR also has a field for the indirect map that shows the entries of source (index) arrays in the AT.

After BACR is assigned to an entry in the AT, SBC monitors the accesses requested for any of the source arrays by checking its indirect map field. When SBC is notified by an access to a source array (e.g., B[i] in Equation (2)), it stores the value of the accessed data in its BACR after performing the required operations in the OT if any operation exists between the source array and the destination array (value). Once an access to the destination array (addr) is seen by SBC, it calculates the base address based on Equation (2) (here B[i] is the value and Addr(A[B[i]]) is the addr). If the same base address is computed multiple times to satisfy a confidence threshold, then SBC sets the base address field of the corresponding entry in the AT and releases the BACR:

$$Addr(A[B[i]]) = BaseAddr(A) + (B[i] \times Size(A)).$$

(2)

Although the element size and base address of the arrays can simply be passed with an instruction, ATP calculates them dynamically to be able to optimize prefetch calculation for different application behaviors. For example, for simple multiplication operation on the index values in an indirect access structure like in the example of A[B[i]\*3], ATP does not need to perform the multiplication. Instead, it can dynamically calculate the size of the array elements three times bigger (which is the stride of the corresponding array accesses). Similarly, an A[B[i]+10] can be represented as A[B[i]] with base\_addr(A[0])+10. This will prevent ATP from using an OT entry to calculate B[i]+10 for each prefetch trigger.

# C. Prefetch Triggering and Calculation

As shown in Figure 4, ATP employs a Prefetch Calculation Unit (PCU) to calculate prefetch addresses when triggered. Prefetch calculation in PCU is performed in two steps: (1) prefetch initialization and (2) prefetch address calculation and issuing of prefetches. Upon an access to a trigger array the ATU signals the PCU to start a prefetching operation. The PCU begins the initialization phase by first allocating an entry for the trigger array in the Prefetch Calculation Buffer (PCB). The PCB is a temporary buffer that keeps detailed information about the entries of potential prefetches. Each entry of PCB has a 1-bit field to show whether the corresponding entry is free for a new task or it is busy calculating a prefetch address. By referring to the ATU tables, the target array/s characteristics are also inserted into the PCB and they are linked to their sources in the PCB entries. Each PCB entry keeps the AT index of the corresponding array, an index pointer that points to the PCB entry of the source array (not used for trigger arrays), and an address field to keep the calculated prefetch addresses. The address field is initialized to the address of the current memory access for trigger arrays, and it is initialized to zero for non-trigger arrays. After the initialization is done, the PCU starts calculating the prefetch addresses for each entry. The address field is updated during prefetch calculation process and the final value of this field is the prefetch address to be issued.

ATP can efficiently calculate prefetch addresses for many different indirect access structures and their combinations. Figure 6 represents each indirect access behavior using a graph model where each entry in the AT is a node and each entry in the IRT is an edge. Since this graph model is in the form of a tree structure, the root of the tree represents the index (trigger) array. A prefetch calculation is performed for each node of this graph. Here, we explain how prefetching is performed for each indirect structure that is shown in Figure 6.

In a multi-level A[B[C[i]]] structure, the index array, C, represents the root node of the graph as shown in Figure 6(a). As ATU signals PCU for prefetching operation on an access to the trigger array C, an entry for C is allocated in the PCB. Since C is the trigger array, by following the indirect

4:12 M. Cavus et al.

Fig. 6. Graph representation of different indirect access behaviors.

Table 3. Prefetch Calculation Steps of A[B[C[i]]] Structure

| Path                            | Step 1                      | Step 2                        | Step 3                     |

|---------------------------------|-----------------------------|-------------------------------|----------------------------|

| С                               | <b>Prefetch</b> C[i+3*dist] |                               |                            |

| $C \rightarrow B$               | Read C[i+2*dist]            | <b>Prefetch</b> B[C[i+2*dist] |                            |

| $C \rightarrow B \rightarrow A$ | Read C[i+1*dist]            | Read B[C[i+1*dist]            | Prefetch A[B[C[i+1*dist]]] |

map fields in the AT, its target array B and then A are also inserted into the PCB and they are linked to their sources in the PCB entries. In our evaluations, the number of PCB entries is equal to the number of AT entries. Using more entries might be useful in case ATP cannot calculate all the prefetches on time and it can insert new entries into PCB before the previous entries are freed. Since we did not observe this in the benchmarks we use, we designed ATP to drop new prefetch tasks if there is no available entry in PCB. To be able to compute independent prefetch addresses concurrently, each PCB entry has its own ALU. After the initialization is done, the PCU starts calculating the prefetch addresses for each entry. To calculate the prefetch address for any non-trigger array, the PCU needs to read a value from the source array. Assuming that we want to calculate a prefetch address for A[B[C[i+dist]]] triggered by an access to C[i], we need to read the value of C[i+dist] and then B[C[i+dist]] to be able to calculate the prefetch address for A[B[C[i+dist]]]. Naturally, to be able to find these (source) values in the cache when needed, they need to be prefetched ahead of time. To be able to prefetch the source values ahead of time, we assign a depth value to each array in the indirect access chain and actual prefetch distance of the corresponding array is calculated by multiplying the depth value with the global prefetch distance of ATP. So for an A[B[C[i]]], a depth-3 indirect structure (the depth of arrays A, B, and C are 1, 2, and 3, respectively), PCU calculates prefetch addresses and performs prefetching for C[i+3\*dist], B[C[i+2\*dist]], and A[B[C[i+1\*dist]]].

In general, an access to a trigger array initiates as many prefetches as there are levels in the indirect structure unless the prefetch address computation fails due to cache misses. Table 3 shows the prefetch calculation steps of an A[B[C[i]]] access structure. Events under the same step for different paths may occur in parallel. For instance, in step1: for path C, we can compute prefetch address for C[i+3\*dist]; for path C $\rightarrow$ B, we can read C[i+2\*dist]; and for path C $\rightarrow$ B $\rightarrow$ A, we can read C[i+1\*dist].

As Table 3 shows, PCU takes the following actions (triggered by an access to C[i]) to perform prefetching for an A[B[C[i]]] structure.

For node C:

Step 1. Compute the prefetch address for C[i+3\*distance] using Equation (3) and issue the prefetch.

Table 4. Prefetch Calculation Steps of A[C[i]] and B[C[i]] Structure

| Path              | Step 1                      | Step 2                        |

|-------------------|-----------------------------|-------------------------------|

| С                 | <b>Prefetch</b> C[i+2*dist] |                               |

| $C \rightarrow A$ | Read C[i+1*dist]            | <b>Prefetch</b> A[C[i+1*dist] |

| $C \rightarrow B$ | Read C[i+1*dist]            | <b>Prefetch</b> B[C[i+1*dist] |

Table 5. Prefetch Calculation Steps of D[A[C[i]]] and B[C[i]] Structure

| Path                            | Step 1                      | Step 2                        | Step 3                            |

|---------------------------------|-----------------------------|-------------------------------|-----------------------------------|

| С                               | <b>Prefetch</b> C[i+3*dist] |                               |                                   |

| $C \rightarrow A$               | Read C[i+2*dist]            | Prefetch A[C[i+2*dist]        |                                   |

| $C \rightarrow B$               | Read C[i+2*dist]            | <b>Prefetch</b> B[C[i+2*dist] |                                   |

| $C \rightarrow A \rightarrow D$ | Read C[i+1*dist]            | Read A[C[i+1*dist]            | <b>Prefetch</b> D[A[C[i+1*dist]]] |

# For node B:

Step 1. Compute the address for C[i+2\*distance] using Equation (3) and read its value from the L1 cache.

Step 2. Compute the prefetch address for B[C[i+2\*distance]] using Equation (2) and issue the prefetch.

For node A:

Step 1. Compute the address for C[i+1\*distance] using Equation (3) and read its value from the L1 cache.

Step 2. Compute the address for B[C[i+1\*distance]] using Equation (2) and read its value from the L1 cache.

Step 3. Compute the prefetch address for A[B[C[i+1\*distance]]] using Equation (2) and issue the prefetch.

$$PfAddr = CurrAddr + (Size \times Depth \times Distance)$$

(3)

Figure 6(b) shows a graph generated from the multi-way indirect access structure of A[C[i]] and B[C[i]]. Since the depth of the tree is 2 in this example, prefetch calculation can be done in two steps as shown in Table 4. The indirect access structure of D[A[C[i]]] and B[C[i]] (both multi-level and multi-way) generates a graph with a depth of 3 as shown in Figure 6(c). The steps of prefetch calculation for this behavior is shown in Table 5. The PCU operation (both initialization and prefetch calculation) for the A[func(B[i])] structure is similar; thus, it is not presented.

Finally, Figure 6(d) shows the graph representation of the indirect access structure of A[B[i][j]], which we classify as having a pointer-type relation. The index array in this structure is a two-dimensional array and it is represented by two separate nodes (i.e., separate entries in the AT). Node B1 represents the first dimension of array B (i.e., the load instruction that reads B[i] and node B2 represents the second dimension (i.e., the load instruction that reads B[i][j]). Also, the edge from B1 to B2 is represented as a pointer type relation instead of a regular type as for the structures discussed above (for Figures 6(a)-6(c)).

In two-dimensional arrays, prefetching can be triggered by two different load accesses (B1 and B2). Table 6 shows the steps of prefetch calculation in an indirect access structure of A[B[i][j]]. Prefetch address calculation is somewhat more complicated for this structure. When ATU observes an access to B1 entry, the prefetch address for B1 is calculated as usual. However, prefetch addresses for B2 and A are not calculated at this moment as the relation type between B1 and B2 is a pointer

4:14 M. Cavus et al.

| Path (1st dimension) | Step 1                          | Step 2                  | Step 3                     |

|----------------------|---------------------------------|-------------------------|----------------------------|

| B1                   | Prefetch B[i+3*dist]            |                         |                            |

|                      | Set root addr in the AT to B[i] |                         |                            |

| Path (2nd dimension) | Step 1                          | Step 2                  |                            |

| B2                   | Read B[i+2*dist]                | Prefetch B[i+2*dist][j] |                            |

| $B2 \rightarrow A$   | Read B[i+1*dist]                | Read B[i+1*dist][j]     | Prefetch A[B[i+1*dist][j]] |

Table 6. Prefetch Calculation Steps of A[B[i][j]] Structure

type. Instead, the root address field of B1 entry in the AT table is updated with the value read by the current access (the value of B[i], which is the address of B[i][0]). Prefetching for entries B2 and A are triggered by the access to the B2 entry. As it is shown in Table 6 when prefetching is triggered by an access to B[i][j], ATP calculates the addresses of B[i+2\*dist][j] and A[B[i+1\*dist][j]]. To be able to calculate the prefetch address for B[i+2\*dist][j], we need to read the address of B[i+2\*dist][0] (i.e., the value of B[i+2\*dist]), which we call the prefetch root address. Using the root address (address of B[i][0]), which was saved previously by trigger B1, we calculate the address of B[i+2\*dist], in which the prefetch root address is stored, by using the first part of Equation (4). Then, we can calculate the prefetch address (address of B[i+2\*dist][j]) using the second part of Equation (4). This calculation is based on the fact that the distance between B[i][0] and B[i][j] should be equal to the distance between B[i+2\*i][0] and B[i+2\*i][j]. Finally, prefetch address calculation for A[B[i+1\*dist][j]] is done in a similar way: It calculates the address of B[i+1\*dist][j]; reads its value and uses it to calculate the prefetch address for A[B[i+1\*dist][j]] as shown in Table 6.

Three-dimensional or more arrays can be represented in ATP, similarly. For example, an indirect access structure with a three-dimensional index array, A[B[i][j][k]], should have 4 AT entries where 3 of them belong to the dimensions of array B and 3 IRT entries where 2 of them have pointer type relations. In this case, prefetches can be triggered by the accesses to B[i], B[i][j], and B[i][j][k] and both B[i] and B[i][j] should be set as root addresses.

Also, it is common to implement 2D arrays by allocating a 1D array and addressing it as a 2D array by calculating the indexes using a width offset (e.g., A[i][j] can be mapped as A[i\*width\_offset+j]). ATP recognizes these as 1D arrays and performs indirect memory prefetch calculations similar to when index array is a 1D array. The support for 2D arrays we mention in this article is for actual 2D arrays, where each element of the first dimension of the array is a pointer to another array.

$$PfRootAddr = RootAddr + (Size \times Depth \times Distance),$$

$$PfAddr = Mem [PfRootAddr] + (AccessedAddress - Mem [RootAddr]). \tag{4}$$

### D. Adaptive Prefetching Distance Selection

Distance Selector (DS) enables ATP to adjust the prefetch distance (in terms of how many array elements ahead) dynamically to be timely accurate on different applications and configurations.

Each power of 2 prefetch distance from 2 to 16 is competed during a test period and at the end of this period, the distance that takes the smallest number of cycles to complete the same number of loop iterations is picked as the distance for the acting period that comes after the testing period. The acting period is a fixed 50 times larger than the testing period. After acting period another testing period follows. In testing period, each prefetch distance is run for a fixed number of loop iterations (64 in our experiments of which the first 32 are used for warm-up and next 32 are used for performance measurement) in a round robin fashion and the number of cycles is counted. DS employs two 32-bit cycle counters. min\_count holds the smallest cycle count and run\_count

holds the cycle count for the currently tested distance. After each distance has completed its test, if run\_count < min\_count, min\_count is set to run\_count and a 3-bit best\_dist register is updated. After all distances are tested, best\_dist indexes a table of 2-bit confidence counters and increments the count for that distance. DS repeats this process until any of the distance's confidence reaches to a threshold that is 2 in our implementation. Using a threshold less than 2 decreases the performance of some applications due to aggressive decisions. Using a threshold above 2 proved useless and increases the duration of the testing phase, which also decreases the performance. Once the decision is made, the chosen distance is set to be used in the acting period and the testing period cycle counters are set to 0.

The ideal warm-up and measurement period may vary based on the previously evaluated distance and the current distance. We can use shorter warmup periods if the current and previous distances are shorter and longer warmup periods if either of them is longer. But in our evaluations, we observed that employing a mechanism to adjust the warmup time does not provide any performance benefit. Our experiments showed that 32 iterations of warmup and 32 iterations of testing period was sufficiently good to find the best distance for all benchmarks.

In multi-core architectures, distance selection is performed separately on each core. We observe that best distances vary for each core running a multi-threaded application due to the sharing of last-level cache and memory bandwidth.

# 2.3 Extending ATP for Prefetching Linked Data Structures

ATP is very successful in prefetching for indirect access structures as we show in the results section. However, for one of our workloads, HJ8, a significant performance opportunity was lost, because indirect accesses were followed by linked list traversals and ATP was not able to capture this behavior. In HJ8, each element of the destination array is a linked list data structure. We extended the ATP to support linked lists. We add three additional fields in the AT: a node bit, node offset and number of nodes. An additional instruction, called atnod is also added to inform the hardware of this behavior and set the fields in the AT. This instruction always follows an ATAR instruction and have two operands: an offset that represent the next field in a linked-node and an immediate value that represents the number of nodes. For example, for a A[B[i]]->next->next structure, where each element of array A is a head node of a linked list where each list has 3 nodes (a head node and two additional nodes), generated ATI sequence is as follows:

```

atar PC_B, atar PC_A, atnod 0 \times 18, 2, atrl PC_B, PC_A, 0.

```

The atnod instruction will set the node bit, node offset and number of nodes fields of the AT table. In this example, atnod suggests that each element of array A points to the head node of a linked list. atnod's first operand (offset) shows that A[B[i]]+0×18 points to the next node of the linked list (A[B[i]]->next). The second operand (which is 2 in this example) shows the number of nodes except for the head node in linked list. Although ATP can stop prefetching nodes if it reaches to the end of the list (where the next node pointer is set to NULL), it requires this information to calculate the depth of prefetches in the chain. When the prefetch is triggered by an access to the index array, B[i], ATP uses the same approach that it does for indirect memory accesses to prefetch future linked node accesses. The steps of prefetch address calculation in this case are shown in Table 7.

For an A[B[i]]->next->next structure, we prefetch the values A[B[i+distance]]-> next->next, A[B[i+distance\*2]]->next, A[B[i+distance\*4]], and B[i+distance\*4]

4:16 M. Cavus et al.

| Path   | Step 1               | Step 2                 | Step 3                              | Step 4                                |

|--------|----------------------|------------------------|-------------------------------------|---------------------------------------|

| В      | Prefetch B[i+4*dist] |                        |                                     |                                       |

| B -> A | Read B[i+3*dist]     | Prefetch A[B[i+3*dist] |                                     |                                       |

| B -> A | Read B[i+2*dist]     | Read A[B[i+2*dist]     | <b>Prefetch</b> A[B[i+2*dist]->next |                                       |

| B -> A | Read B[i+1*dist]     | Read A[B[i+1*dist]     |                                     | Prefetch A[B[i+1*dist] -> next-> next |

Table 7. Prefetch Calculation Steps of A[B[i]] Structure Where Each Element of Array A Is a Linked List

simultaneously. In this case, if A[B[i+distance\*2]] is not in the cache (due to a late prefetch, etc.), then ATP can drop the prefetch for array A[B[i+distance\*2]]->next but still can issue the rest of the prefetches. Instead of aggressively prefetching for each level, it drops if the prefetches are not timely accurate and try to set the distance accordingly. Although using this method requires redundant calculations, we perform the address calculations of each level simultaneously by using a separate ALU for each PCB entry instead of having a separate mechanism to keep track of all incoming prefetched data and scheduling future prefetches. This mechanism might be useful for an event-based system like ETP but in our evaluations, we observed that the pipelined prefetching method performs better with ATP on the benchmarks we used.

ATP can calculate prefetches for longer linked lists, but if the linked list is too long, then it is difficult to find an optimal distance value at which the prefetches for the index array will not be early and the prefetches for the last node of the linked list will not be too late. This is also an issue with ETP, however.

We observe significant performance improvement in HJ8 with an ATP that supports linked list traversals. Without this support, ATP achieves a speedup of 1.44 for this benchmark by successfully prefetching the indirect accesses. With the added linked list support, ATP boosts the speedup to 3.32 (2.3× speedup over ATP without linked-list support). By contrast, software prefetching, SWPF, that prefetch for both indirect accesses and the linked list in HJ8 could only achieve a speedup of 1.65, which is much lower than ATP's performance. It is important to note, however, that our implementation is limited to cases where number of nodes are known. HJ8 has 3 nodes for all the linked lists so prefetch depth is constant (e.g., depth is 4 in the example in Table 7) and ATP does not need to predict depth (distance, however, is dynamically evaluated as before). When the number of nodes is not known, ATP must make predictions for depth of the structure, which complicates the hardware mechanism. The situation is further complicated, because unless searching of keys in hash-join buckets are pre-executed to determine if the next node has to be prefetched, many unnecessary prefetches are to be issued, which is also the case for ETP. This scenario is not evaluated and left as future work, since our focus in this article is indirect access structures.

#### 3 EXPERIMENTAL SETUP

We now discuss details of the simulation infrastructure, the workloads, and the configurations that we used for our evaluation.

#### 3.1 Simulation Environment

We implemented the ATP on the gem5 simulator [46] using System call Emulation (SE) mode (which does not simulate page-table walk) and generated the results using the x86 out-of-order CPU model. The SE mode only runs statically linked binaries, because it emulates system calls without Operating System. TLB faults and misses are also handled by software (via emulated

| ISA               | 64-bit x86                                                              |

|-------------------|-------------------------------------------------------------------------|

| Number of Cores   | 1-8                                                                     |

| Architecture      | 4-Issue, Out-Order, 2 GHz                                               |

| LQ/SQ Entries     | 64/36                                                                   |

| ROB Entries       | 168                                                                     |

| Branch Pred.      | Tournament BP                                                           |

| L1 Cache          | Private, 8-way 32 KB, MSHRs: 8, latency: 4 cycles                       |

| L2 Cache          | Private, 8-way 256 KB, MSHRs: 16, latency: 12 cycles                    |

| L3 Cache          | Shared, 16-way, 1 MB per core, MSHRs: 16, latency: 32 cycles            |

| Memory            | DDR3-1600, 800 MHz, 1 channel, 2 ranks, 8 banks/rank, 512K              |

|                   | rows/bank, 1 kB row, baseline $t_{RCD}/t_{RAS}/t_{WR}$ : 13.75/35/15 ns |

| Memory Controller | 64-entry RD/WR request queue, FR-FCFS scheduling, closed-row            |

|                   | policy                                                                  |

Table 8. Simulator Configurations

Table 9. Hardware Budget of ATP on Single-core Architecture

|                                            | ATI   | Array | Relation | Operation | Prefetch | Stream   | Size Calc. | Base Calc. | Distance |  |

|--------------------------------------------|-------|-------|----------|-----------|----------|----------|------------|------------|----------|--|

|                                            | Queue | Table | Table    | Table     | Table    | Register | Reg.       | Reg.       | Selector |  |

| # of Entries                               | 4     | 4     | 4        | 2         | 4        | 1        | 1          | 1          | -        |  |

| Entry size (bits)                          | 80    | 268   | 6        | 39        | 69       | 101      | 172        | 105        | 118      |  |

| <b>Total Size:</b> 2,266 bits (~284 bytes) |       |       |          |           |          |          |            |            |          |  |

system calls), so all the detailed overhead related to the TLB are removed from the critical path of execution of the target machine and binary.

Table 8 shows the configuration of each core while Table 9 shows the ATP configuration. We inserted ATI instructions at the beginning of the loop and implemented ATP to prefetch for the L1 cache to provide for a direct comparison with IMP [3], which prefetches for the L1 cache. Each L1 is equipped with an 8-enty prefetch request queue (PRQ) in our evaluation. In all methods tested, computed prefetch addresses are placed into the PRQ before they are issued to the L1 cache.

As we described in Section 2.2.2.C, the prefetch address calculation depends on reading source array values from the L1 cache. In our evaluation, we assume that the ATP has dedicated ports to access the data TLB and the L1 data cache. If in any of the prefetch address calculation steps the source values cannot be read due to a data TLB or an L1 data cache miss, then the process of prefetch calculation and issuing is aborted until another access to the trigger array occurs and PCU is notified for initialization.

We faithfully implemented IMP (attached to each L1 cache) on our baseline architecture. Similar as in Reference [3], our IMP implementation used a 16-entry Prefetch Table and a 4-entry Indirect Pattern Detector with 4-base address length and 4 shift values. Total hardware budget for our IMP implementation was 8,032 bits (1,004 bytes) per core, almost four times the size of the ATP (see Table 9). To evaluate the performance of software prefetching, we inserted software prefetching instructions inside the loops containing the indirect memory accesses. For both IMP and software prefetching, we measured the speedup for various prefetch distances but only report the results for the best performing distance.

For each benchmark, we fast-forward to the beginning of the loop containing indirect memory accesses and simulate 100M instructions after warming up for 10M instructions; for multi-core

4:18 M. Cavus et al.

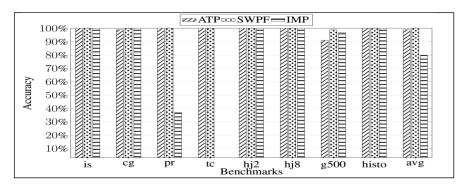

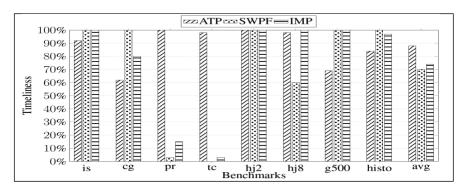

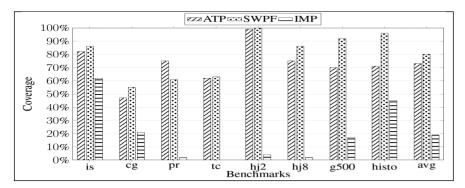

simulations, each core simulates at least 100M instructions. For the multi-core simulations, we run the multi-threaded version of the benchmarks where the number of threads is equal to the number of cores. In our simulations, we did not use warm-up, however, we expect the simulation results would not be significantly affected by it.