#### UNIVERSITY OF MINNESOTA

This is to certify that I have examined this copy of a doctoral dissertation by

Brent Goplen

and have found that it is complete and satisfactory in all respects, and that any and all revisions required by final examining committee have been made.

Professor Sachin S. Sapatnekar

Name of the Faculty Advisor

Signature of the Faculty Advisor

Date

GRADUATE SCHOOL

## Advanced Placement Techniques for Future VLSI Circuits

#### A DISSERTATION SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA BY

Brent Goplen

#### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Sachin S. Sapatnekar, Advisor

October 2006

© Brent Goplen 2006

## Acknowledgements

First of all, I would like to express my deepest gratitude to my advisor, Professor Sachin Sapatnekar, for his guidance and support though my graduate studies. Over the many years that he has been my advisor, he has served as an incredible inspiration and talented mentor in my educational and career development. His keen insights, direction, and persistent encouragement were instrumental in my success in solving tough technical problems. It has truly been a pleasure and an honor working with him.

I would also like to thank Professor Kia Bazargan, Professor Chris Kim, and Professor Antonia Zhai for reviewing my thesis and serving on my Ph.D. defense committee.

I am grateful to Dr. Prashant Saxena for mentoring me during my internship at Intel Labs (CAD Research) and contributing to the work on repeater count reduction. I would also like to thank T. Cao, A. Chowdhary, K. Rajagopal, B. Velikandanathan, D. Kirkpatrick, and P. Cocchini for their support while at Intel.

I owe many thanks to my colleagues in the VEDA Lab and the University of Minnesota for their help and many meaningful discussions: Rupesh, Shrirang, Venkat, Hongliang, Haifeng, Jaski, Tianpei, Sagar, Yong, Yan, Anup, Sanjay, Qunzeng, Baktash, Saeed, Pongstorn, Hushrav, and many others.

I am also grateful to the Semiconductor Research Corporation for funding my graduate studies through an SRC fellowship.

Finally, I would like to thank my family for their continued support and encouragement though the years.

## Abstract

The design of future VLSI circuits is becoming more difficult in advanced technologies, and additional design constraints need to be considered in electronic design automation (EDA) tools. These new complexities are linked to the industry-wide trend of technology scaling along a Moore's law trajectory. The enhanced integration densities predicted by Moore's law may be achieved through two approaches: first, by decreasing the feature sizes, to allow a larger number of transistors to be accommodated in a smaller area, and second, through new technologies such as three-dimensional (3D) integration, which stack multiple active layers into a monolithic chip, thereby increasing the number of transistors per unit footprint.

A number of new challenges arise in the design of 3D circuits. These circuits have significantly larger power densities than their 2D counterparts and high thermal resistances between active layers. Unless 3D circuits are carefully designed, they can face severe thermal problems that can reduce their performance and reliability. A second important design concern in 3D ICs is related to the bottleneck in connecting wires between active layers: the maximum allowable density of interlayer vias is greatly restricted due to fabrication limitations.

Another issue that arises in the design of advanced VLSI circuits is related to the problem of interconnect delays. As feature sizes decrease, interconnect delays scale poorly, and must be managed: the delay of an interconnect wire increases quadratically with its length, but through appropriate repeater insertion, this dependency can be brought down from quadratic to linear. However, trends show that the number of repeaters will increase exponentially in future technology generations. Without methods to manage and reduce repeater counts, a breakdown in the design process could result due to the perturbations introduced by repeater insertion.

Several aspects of performance-driven physical design at and around the placement stage are examined in this thesis to address these issues that arise in the design of nextgeneration circuits. First, placement techniques for 3D ICs are developed, addressing the issue of interlayer via density limitations. It is observed that a tradeoff exists between the number of interlayer vias and wirelength for 3D ICs, and placement and legalization methods are developed using analytical and partitioning-based techniques to minimize both wirelength and interlayer via densities. This allows the wirelengths to be minimized for any desired interlayer via density that can be realized with the given fabrication Thermal placement and legalization are then used to reduce thermal technology. problems by judiciously placing standard cells, the primary sources of heat, within the chip. By using net weighting and additional thermal-directing nets in partitioning-based placement, nets are arranged and cells placed to reduce both power and temperature. During detailed placement, thermal considerations are retained to minimize degradation and make improvements based on the thermal objective. Next, an algorithm for reducing thermal problems in 3D ICs, through the insertion of thermal vias into placed designs, is developed. Thermal vias serve no electrical function, but are used for heat removal from the chip. Using temperature simulations obtained with finite element analysis (FEA), the arrangement of thermal vias is iteratively adjusted until the thermal objective is achieved, with minimal thermal via usage. Finally, a method for ameliorating the increasing number of repeaters, caused by scaling, is developed. This part is primarily directed towards the design of 2D chips, although the basic principles are also applicable to 3D designs. Repeater counts are reduced by dynamically modifying net weights in a contextsensitive manner during global placement and coarse legalization with layer assignment as well as valid inter-repeater distance ranges being modeled.

## Contents

| 1 | I INTRODUCTION                                                                                | 1  |

|---|-----------------------------------------------------------------------------------------------|----|

| 2 | 2 THREE-DIMENSIONAL INTEGRATION                                                               | 4  |

|   | 2.1 BENEFITS AND OBSTACLES                                                                    | 5  |

|   | 2.2 FABRICATION TECHNOLOGIES                                                                  |    |

| 3 | 3 TEMPERATURE CALCULATION                                                                     | 8  |

|   | 3.1 INTRODUCTION                                                                              |    |

|   | 3.2 FEA BACKGROUND                                                                            |    |

|   | 3.3 CONDUCTIVE STAMP                                                                          |    |

|   | 3.4 CONVECTIVE STAM                                                                           |    |

|   | 3.5 ELEMENT MESH AND GLOBAL MATRIX                                                            |    |

|   | 3.6 ISOTHERMIC BOUNDARY CONDITIONS                                                            |    |

| 4 |                                                                                               |    |

| - | 4.1 INTRODUCTION                                                                              |    |

|   | 4.2 Force-Directed Placement Methods                                                          |    |

|   | 4.3 PARTITIONING PLACEMENT                                                                    |    |

|   | 4.4 LEGALIZATION AND DETAILED PLACEMENT                                                       |    |

| _ |                                                                                               |    |

| 5 |                                                                                               |    |

|   | 5.1 INTRODUCTION                                                                              |    |

|   | 5.2 GLOBAL PLACEMENT                                                                          |    |

|   | 5.3 COARSE LEGALIZATION                                                                       |    |

|   | 5.3.1 Cell Shifting                                                                           |    |

|   | 5.3.2 Local Moves                                                                             |    |

|   | <ul><li>5.3.2.1 Efficient Cost Reduction Calculation</li><li>5.3.2.2 Implementation</li></ul> |    |

|   | 5.3.3 Global Moves                                                                            |    |

|   | 5.3.3.1 Target Region                                                                         |    |

|   | 5.3.3.2 Implementation                                                                        |    |

|   | 5.3.4 Implementation                                                                          |    |

|   | 5.4 FINAL LEGALIZATION                                                                        | 41 |

|   | 5.4.1 External Capacities                                                                     | 41 |

|   | 5.4.2 Target Regions                                                                          |    |

|   | 5.4.3 Implementation                                                                          | 46 |

|   | 5.5 POST-OPTIMIZATION                                                                         |    |

|   | 5.6 IMPLEMENTATION                                                                            |    |

|   | 5.7 Results                                                                                   |    |

|   | 5.7.1 Tradeoff between Interlayer Via Count and Wirelength                                    |    |

|   | 5.7.2 The Effect of Layer Count                                                               |    |

|   | 5.7.3 The Effect of Post-Optimization                                                         |    |

|   | 5.7.4 Run-Time Analysis                                                                       |    |

|   | 5.8 CONCLUSIONS                                                                               |    |

| 6 |                                                                                               |    |

|   | 6.1 INTRODUCTION                                                                              |    |

|   | 6.2 THERMAL OBJECTIVE FUNCTION                                                                |    |

|   | 6.3 GLOBAL PLACEMENT                                                                          |    |

|   | 6.3.1 Thermal-Aware Net Weighting                                                             |    |

| 6.3.3       Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 6.3.2    | Thermal Resistance Reduction Nets                     | 71  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|-------------------------------------------------------|-----|

| 6.5       IMPLEMENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 6.3.3    | Implementation                                        | 74  |

| 6.6       RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 6.4 LEG  | ALIZATION                                             | 75  |

| 6.6.1       Interlayer Via Coefficient Versus Thermal Coefficient       79         6.6.2       The Effect of Number of Layers on Thermal Placement       87         6.6.3       Thermal Placement of Various Benchmarks       90         6.7       CONCLUSIONS       97         7       THERMAL VIA PLACEMENT IN 3D ICS       99         7.1       INTRODUCTION       99         7.2       THERMAL VIAS       99         7.3       THERMAL VIAS       102         7.4       ITERATIVE THERMAL VIA METHOD       105         7.4.1       Updating the Thermal Conductivities       106         7.4.2       Thermal Via Density       109         7.5       IMPLEMENTATION       111         7.6       RESULTS       113         7.6.1       Using Uniform Thermal Via Densities       116         7.6.2       Thermal Gradient Objectives       117         7.6.3       Temperature Objectives       121         7.6.4       Thermal Profile of Struct       126         7.7       Conclusion       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT       130         8.1       Introduction       133         8.3       PROPOSED APPROACH<                                           |   | 6.5 IMP  | LEMENTATION                                           | 75  |

| 6.6.2       The Effect of Number of Layers on Thermal Placement.       87         6.6.3       Thermal Placement of Various Benchmarks       90         6.7       CONCLUSIONS       97         7       THERMAL VIA PLACEMENT IN 3D ICS       99         7.1       INTRODUCTION       99         7.2       THERMAL VIA PLACEMENT IN 3D ICS       99         7.3       THERMAL VIA PLACEMENT IN 3D ICS       99         7.4       INTRODUCTION       99         7.3       THERMAL VIA REGIONS       102         7.4       ITERMAL VIA METHOD       105         7.4.1       Updating the Thermal Conductivities       106         7.4.2       Thermal Via Density       109         7.5       IMPLEMENTATION       111         7.6       RESULTS       113         7.6.1       Using Uniform Thermal Via Densities       116         7.6.2       Thermal Gradient Objectives       117         7.6.3       Temperature Objectives       119         7.6.4       Thermal Via Density Objectives       121         7.6.5       Comparing Different Objectives       123         7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct                                                           |   | 6.6 Res  | ULTS                                                  | 76  |

| 6.6.2       The Effect of Number of Layers on Thermal Placement.       87         6.6.3       Thermal Placement of Various Benchmarks       90         6.7       CONCLUSIONS       97         7       THERMAL VIA PLACEMENT IN 3D ICS       99         7.1       INTRODUCTION       99         7.2       THERMAL VIA PLACEMENT IN 3D ICS       99         7.3       THERMAL VIA PLACEMENT IN 3D ICS       99         7.4       INTRODUCTION       99         7.3       THERMAL VIA REGIONS       102         7.4       ITERMAL VIA METHOD       105         7.4.1       Updating the Thermal Conductivities       106         7.4.2       Thermal Via Density       109         7.5       IMPLEMENTATION       111         7.6       RESULTS       113         7.6.1       Using Uniform Thermal Via Densities       116         7.6.2       Thermal Gradient Objectives       117         7.6.3       Temperature Objectives       119         7.6.4       Thermal Via Density Objectives       121         7.6.5       Comparing Different Objectives       123         7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct                                                           |   | 6.6.1    | Interlayer Via Coefficient Versus Thermal Coefficient | 79  |

| 6.6.3       Thermal Placement of Various Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 6.6.2    |                                                       |     |

| 6.7       CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 6.6.3    |                                                       |     |

| 7.1       INTRODUCTION.       99         7.2       THERMAL VIAS       99         7.3       THERMAL VIA REGIONS       102         7.4       ITERATIVE THERMAL VIA METHOD.       105         7.4.1       Updating the Thermal Conductivities.       106         7.4.2       Thermal Via Density.       109         7.5       IMPLEMENTATION       111         7.6       RESULTS.       113         7.6.1       Using Uniform Thermal Via Densities       116         7.6.2       Thermal Gradient Objectives.       117         7.6.3       Temperature Objectives.       119         7.6.4       Thermal Via Density Objectives.       121         7.6.5       Comparing Different Objectives.       123         7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct.       126         7.7       CONCLUSION       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT.       130         8.1       INTRODUCTION.       133         8.3.1       Threshold-based Net-weighting.       133         8.3.1       Threshold-based Net-weighting.       135         8.3.2       Layer Transitions.       137                                                          |   | 6.7 Con  |                                                       |     |

| 7.2       THERMAL VIAS       99         7.3       THERMAL VIA REGIONS       102         7.4       ITERATIVE THERMAL VIA METHOD       105         7.4.1       Updating the Thermal Conductivities       106         7.4.2       Thermal Via Density       109         7.5       IMPLEMENTATION       111         7.6       RESULTS       113         7.6.1       Using Uniform Thermal Via Densities       116         7.6.2       Thermal Gradient Objectives       117         7.6.3       Temperature Objectives       117         7.6.4       Thermal Oradient Objectives       121         7.6.5       Comparing Different Objectives       123         7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct       126         7.7       CONCLUSION       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT       130         8.1       INTRODUCTION       133         8.3.1       Threshold-based Net-weighting       133         8.3.2       Layer Transitions       137         8.3.1       Threshold-based Net-weighting       137         8.4       IMPLEMENTATION       139      <                                                                  | 7 | THERM    | AL VIA PLACEMENT IN 3D ICS                            | 99  |

| 7.3       THERMAL VIA REGIONS       102         7.4       ITERATIVE THERMAL VIA METHOD       105         7.4.1       Updating the Thermal Conductivities       106         7.4.2       Thermal Via Density       109         7.5       IMPLEMENTATION       111         7.6       RESULTS       116         7.6.2       Thermal Via Densities       116         7.6.2       Thermal Gradient Objectives       117         7.6.3       Temperature Objectives       119         7.6.4       Thermal Via Density Objectives       121         7.6.5       Comparing Different Objectives       123         7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct       126         7.7       CONCLUSION       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT       130         8.1       INTRODUCTION       130         8.2       PLACEMENT INFRASTRUCTURE       131         8.3       PROPOSED APPROACH       133         8.3.1       Threshold-based Net-weighting       135         8.3.2       Layer Transitions       137         8.4       IMPLEMENTATION       139 <t< td=""><td></td><td>7.1 INTI</td><td>RODUCTION</td><td>99</td></t<>              |   | 7.1 INTI | RODUCTION                                             | 99  |

| 7.4       ITERATIVE THERMAL VIA METHOD.       105         7.4.1       Updating the Thermal Conductivities.       106         7.4.2       Thermal Via Density.       109         7.5       IMPLEMENTATION       111         7.6       RESULTS.       113         7.6.1       Using Uniform Thermal Via Densities       116         7.6.2       Thermal Gradient Objectives       117         7.6.3       Temperature Objectives       119         7.6.4       Thermal Via Density Objectives       121         7.6.5       Comparing Different Objectives       123         7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct       126         7.7       CONCLUSION       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT       130         8.1       INTRODUCTION       130         8.3       PLACEMENT INFRASTRUCTURE       131         8.3.3       PROPOSED APPROACH       133         8.3.1       Threshold-based Net-weighting       135         8.3.2       Layer Transitions       137         8.4       IMPLEMENTATION       139         8.5       EXPERIMENTAL RESULTS       139 </td <td></td> <td>7.2 The</td> <td>RMAL VIAS</td> <td>99</td> |   | 7.2 The  | RMAL VIAS                                             | 99  |

| 7.4.1       Updating the Thermal Conductivities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 7.3 The  | RMAL VIA REGIONS                                      |     |

| 7.4.2       Thermal Via Density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 7.4 ITEF | AATIVE THERMAL VIA METHOD                             | 105 |

| 7.5       IMPLEMENTATION       111         7.6       RESULTS       113         7.6.1       Using Uniform Thermal Via Densities       116         7.6.2       Thermal Gradient Objectives       117         7.6.3       Temperature Objectives       119         7.6.4       Thermal Via Density Objectives       121         7.6.5       Comparing Different Objectives       123         7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct       126         7.7       CONCLUSION       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT       130         8.1       INTRODUCTION       130         8.2       PLACEMENT INFRASTRUCTURE       131         8.3.1       Threshold-based Net-weighting       133         8.3.2       Layer Transitions       137         8.4       IMPLEMENTATION       139         8.5       EXPERIMENTAL RESULTS       139         8.6       CONCLUSION       147                                                                                                                                                                                                                                                          |   | 7.4.1    | Updating the Thermal Conductivities                   | 106 |

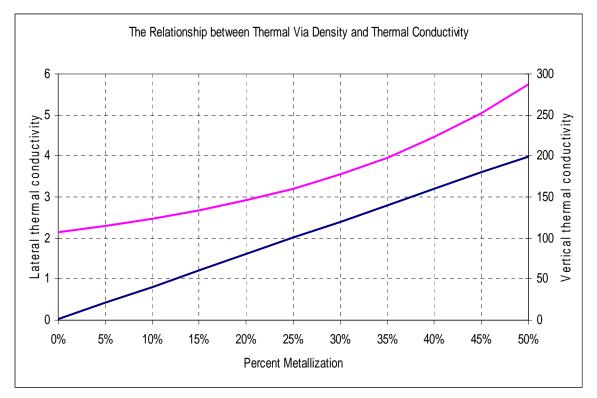

| 7.6       RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 7.4.2    | Thermal Via Density                                   | 109 |

| 7.6.1       Using Uniform Thermal Via Densities       116         7.6.2       Thermal Gradient Objectives       117         7.6.3       Temperature Objectives       119         7.6.4       Thermal Via Density Objectives       121         7.6.5       Comparing Different Objectives       123         7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct       126         7.7       CONCLUSION       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT       130         8.1       INTRODUCTION       130         8.2       PLACEMENT INFRASTRUCTURE       131         8.3       PROPOSED APPROACH       133         8.3.1       Threshold-based Net-weighting.       135         8.3.2       Layer Transitions.       137         8.4       IMPLEMENTATION       139         8.5       EXPERIMENTAL RESULTS       139         8.6       CONCLUSIONS       148                                                                                                                                                                                                                                                                                        |   | 7.5 IMP  | LEMENTATION                                           | 111 |

| 7.6.2       Thermal Gradient Objectives       117         7.6.3       Temperature Objectives       119         7.6.4       Thermal Via Density Objectives       121         7.6.5       Comparing Different Objectives       123         7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct       126         7.7       CONCLUSION       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT       130         8.1       INTRODUCTION       130         8.2       PLACEMENT INFRASTRUCTURE       131         8.3       PROPOSED APPROACH       133         8.3.1       Threshold-based Net-weighting       135         8.3.2       Layer Transitions       137         8.4       IMPLEMENTATION       139         8.5       EXPERIMENTAL RESULTS       139         8.6       CONCLUSIONS       148                                                                                                                                                                                                                                                                                                                                                            |   | 7.6 Res  | ULTS                                                  | 113 |

| 7.6.3       Temperature Objectives       119         7.6.4       Thermal Via Density Objectives       121         7.6.5       Comparing Different Objectives       123         7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct       126         7.7       CONCLUSION       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT       130         8.1       INTRODUCTION       130         8.2       PLACEMENT INFRASTRUCTURE       131         8.3       PROPOSED APPROACH       133         8.3.1       Threshold-based Net-weighting       135         8.3.2       Layer Transitions       137         8.4       IMPLEMENTATION       139         8.5       EXPERIMENTAL RESULTS       139         8.6       CONCLUSIONS       147                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 7.6.1    | Using Uniform Thermal Via Densities                   | 116 |

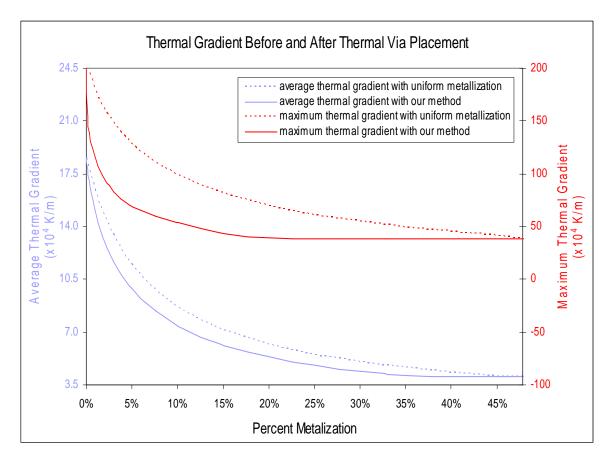

| 7.6.4       Thermal Via Density Objectives       121         7.6.5       Comparing Different Objectives       123         7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct       126         7.7       CONCLUSION       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT       130         8.1       INTRODUCTION       130         8.2       PLACEMENT INFRASTRUCTURE       131         8.3       PROPOSED APPROACH       133         8.3.1       Threshold-based Net-weighting       135         8.3.2       Layer Transitions       139         8.5       EXPERIMENTAL RESULTS       139         8.6       CONCLUSION       148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 7.6.2    | Thermal Gradient Objectives                           | 117 |

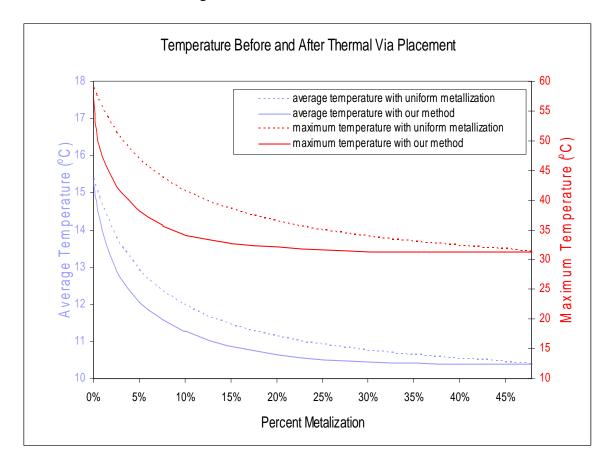

| 7.6.5       Comparing Different Objectives.       123         7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct.       126         7.7       CONCLUSION       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT.       130         8.1       INTRODUCTION.       130         8.2       PLACEMENT INFRASTRUCTURE       131         8.3       PROPOSED APPROACH.       133         8.3.1       Threshold-based Net-weighting.       135         8.3.2       Layer Transitions.       137         8.4       IMPLEMENTATION       139         8.5       EXPERIMENTAL RESULTS       139         8.6       CONCLUSIONS.       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 7.6.3    | Temperature Objectives                                | 119 |

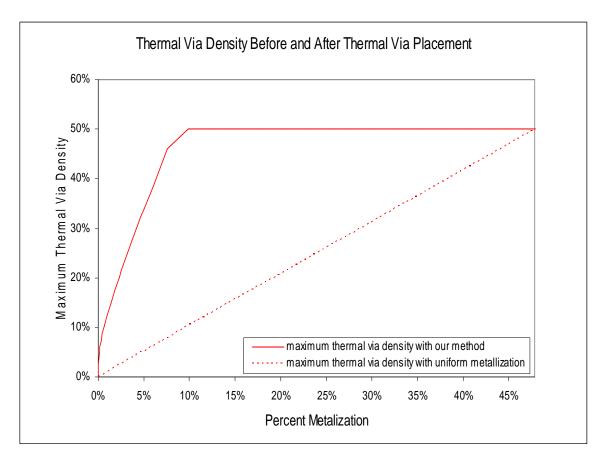

| 7.6.6       Run Time       125         7.6.7       Thermal Profile of Struct.       126         7.7       CONCLUSION       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT.       130         8.1       INTRODUCTION.       130         8.2       PLACEMENT INFRASTRUCTURE       131         8.3       PROPOSED APPROACH.       133         8.3.1       Threshold-based Net-weighting.       135         8.3.2       Layer Transitions.       137         8.4       IMPLEMENTATION       139         8.5       EXPERIMENTAL RESULTS       139         8.6       CONCLUSIONS.       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 7.6.4    | Thermal Via Density Objectives                        | 121 |

| 7.6.7       Thermal Profile of Struct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 7.6.5    | Comparing Different Objectives                        | 123 |

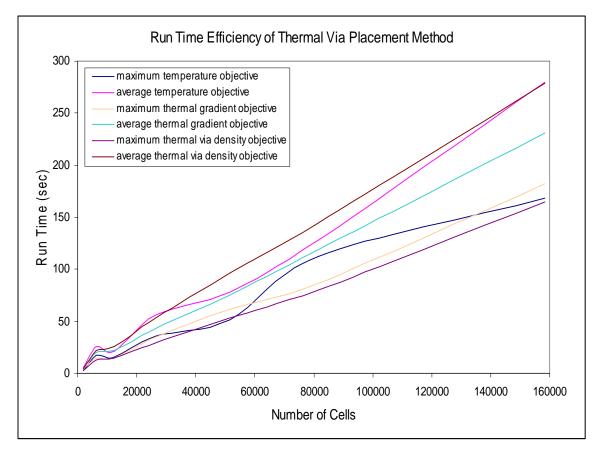

| 7.7       CONCLUSION       128         8       NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT       130         8.1       INTRODUCTION       130         8.2       PLACEMENT INFRASTRUCTURE       131         8.3       PROPOSED APPROACH       133         8.3.1       Threshold-based Net-weighting       135         8.3.2       Layer Transitions       137         8.4       IMPLEMENTATION       139         8.5       EXPERIMENTAL RESULTS       139         8.6       CONCLUSIONS       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 7.6.6    | Run Time                                              | 125 |

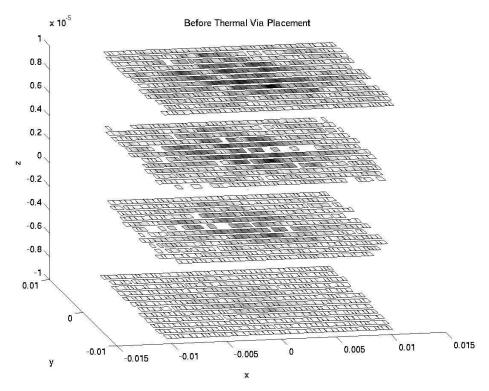

| 8         NET WEIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 7.6.7    | Thermal Profile of Struct                             | 126 |

| 8.1       INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 7.7 Con  | ICLUSION                                              | 128 |

| 8.2       PLACEMENT INFRASTRUCTURE       131         8.3       PROPOSED APPROACH       133         8.3.1       Threshold-based Net-weighting       135         8.3.2       Layer Transitions       137         8.4       IMPLEMENTATION       139         8.5       EXPERIMENTAL RESULTS       139         8.6       CONCLUSION       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8 | NET WI   | EIGHTING TO REDUCE REPEATER COUNTS DURING PLACEMENT   | 130 |

| 8.3       PROPOSED APPROACH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 8.1 INTE | RODUCTION                                             | 130 |

| 8.3.1       Threshold-based Net-weighting.       135         8.3.2       Layer Transitions.       137         8.4       IMPLEMENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 8.2 PLA  | CEMENT INFRASTRUCTURE                                 | 131 |

| 8.3.2       Layer Transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 8.3 Pro  | POSED APPROACH                                        | 133 |

| 8.4       IMPLEMENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 8.3.1    | Threshold-based Net-weighting                         | 135 |

| 8.5       EXPERIMENTAL RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 8.3.2    | Layer Transitions                                     | 137 |

| 8.6       CONCLUSION       147         9       CONCLUSIONS       148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 8.4 IMP  | LEMENTATION                                           | 139 |

| 9 CONCLUSIONS148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 8.5 EXP  | ERIMENTAL RESULTS                                     | 139 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 8.6 CON  | ICLUSION                                              | 147 |

| REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9 | CONCL    | USIONS                                                | 148 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R | EFERENC  | ES                                                    |     |

## **List of Tables**

| Table 1. Benchmark Circuits                                                                                                                                                                                                              | .50  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 2. Wirelength for ibm01 to ibm18 as the interlayer via coefficient is varied                                                                                                                                                       | .53  |

| Table 3. Interlayer via counts for ibm01 to ibm18 as the interlayer via coefficient is varied                                                                                                                                            | .54  |

| Table 4. Tradeoff between wirelength and interlayer via count for ibm01                                                                                                                                                                  | .56  |

| Table 5. Runtime composition for benchmarks ibm01 to ibm18.                                                                                                                                                                              | .62  |

| Table 6. Tradeoff between runtime and quality for benchmarks ibm01 to ibm18                                                                                                                                                              | .62  |

| Table 7. Benchmark Circuits                                                                                                                                                                                                              | .76  |

| Table 8. Thermal Conductivity of Vias and Interconnects                                                                                                                                                                                  | .77  |

| Table 9. Thermal Conductivity of Individual Levels                                                                                                                                                                                       | .78  |

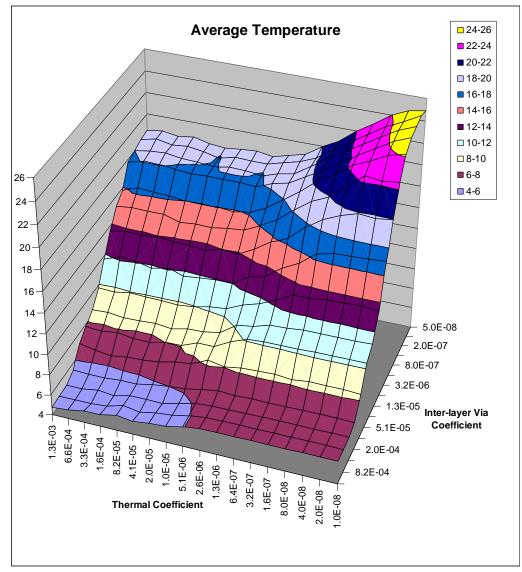

| Table 10. The effect of thermal placement on the average temperature of ibm01                                                                                                                                                            | .81  |

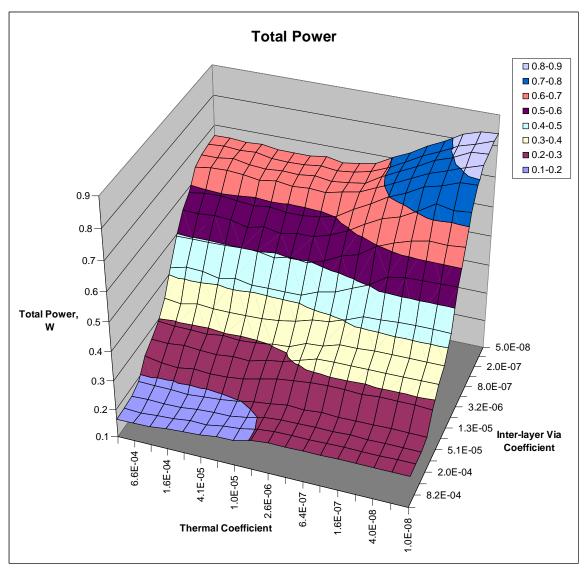

| Table 11. The effect of thermal placement on the total power of ibm01                                                                                                                                                                    | .82  |

| Table 12. The effect of thermal placement on the maximum temperature of ibm01                                                                                                                                                            | .83  |

| Table 13. The effect of thermal placement on the wirelength of ibm01                                                                                                                                                                     | .84  |

| Table 14. The effect of thermal placement on the interlayer via count of ibm01                                                                                                                                                           | .85  |

| Table 15. The percent change in the average temperature, maximum temperature, total power, wirelength, and interlayer via counts for ibm01 from a thermal coefficient of $1 \times 10^{-8}$ to a value of $4.1 \times 10^{-5}$ for ibm01 | .86  |

| Table 16. Average temperature for thermal placements of the benchmark circuits                                                                                                                                                           | .91  |

| Table 17. Maximum temperature for thermal placements of the benchmark circuits                                                                                                                                                           | .92  |

| Table 18. Total power for thermal placements of the benchmark circuits                                                                                                                                                                   | .93  |

| Table 19. Wirelength for thermal placements of the benchmark circuits                                                                                                                                                                    | .94  |

| Table 20. Interlayer via counts for thermal placements of the benchmark circuits                                                                                                                                                         | .95  |

| Table 21. Thermal Conductivities of Thermal Vias Regions                                                                                                                                                                                 | .110 |

| Table 22. Benchmark Circuits                                                                                                                                                                                                             | .114 |

| Table 23. Thermal Properties with a Uniform Distribution of Thermal Via Densities                                                                                                                                                        | .116 |

| Table 24. Optimization to Maximum Thermal Gradient                                                                                                                                                                                       | .119 |

| Table 25. Optimization to Average Thermal Gradient                                                                                                                                                                                       | .119 |

| Table 26. Optimization to Maximum Temperature                                                                                                                                                                                            | .121 |

| Table 27. Optimization to Average Temperature                                                                                                                                                                                            | .121 |

| Table 28. Optimization to Maximum Thermal Via Density                                                                                                                                                                                    | .122 |

| Table 29. Optimization to Average Thermal Via Density                            | .123 |

|----------------------------------------------------------------------------------|------|

| Table 30. Summary of Results for Different Objectives                            | .124 |

| Table 31. The Results compared to the Minimum Case                               | .125 |

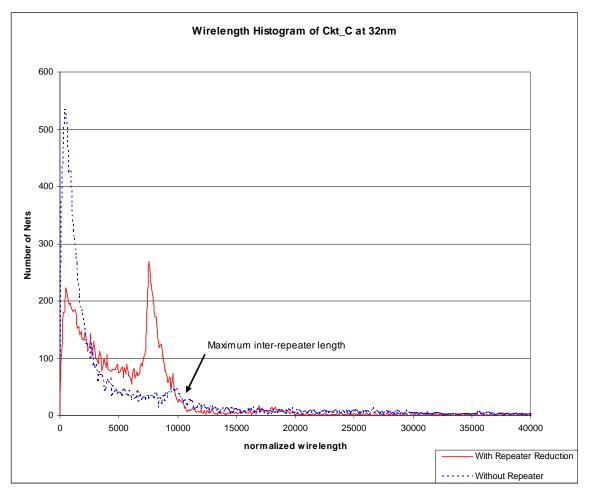

| Table 32. Testcases used for repeater count reduction experiments                | .141 |

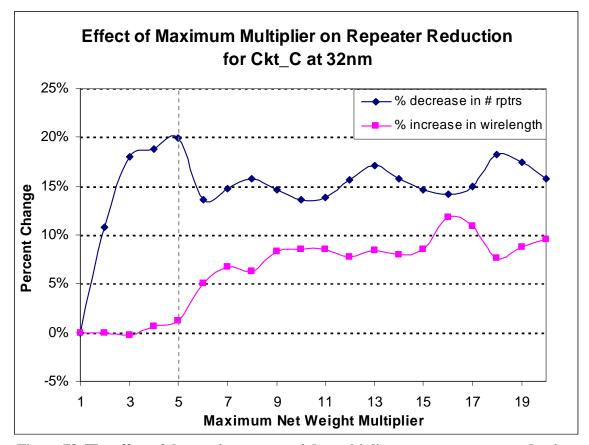

| Table 33. Comparing function types at the 32nm node for repeater count reduction | .141 |

| Table 34. Comparing repeater count reduction at 32 nm.                           | .143 |

| Table 35. Comparing repeater count reduction at 45 nm.                           | .143 |

# **List of Figures**

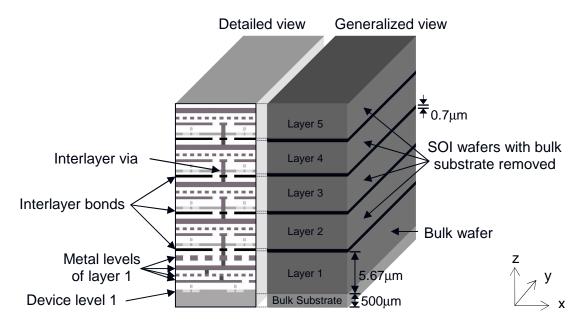

| Figure 1. Composition of a 3D IC (adapted from [4])                                | 4  |

|------------------------------------------------------------------------------------|----|

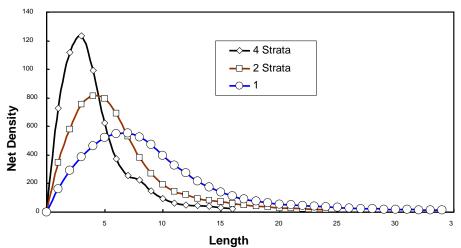

| Figure 2. Improvement in the wirelength for 3D ICs from [9]                        | 5  |

| Figure 3. An eight-node hexahedral element.                                        | 8  |

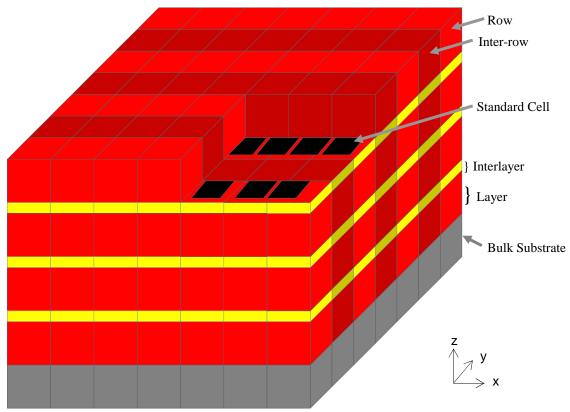

| Figure 4. Mesh of a 3D IC.                                                         | 12 |

| Figure 5. 3D global placement algorithm                                            | 24 |

| Figure 6. Region partitioning algorithm for 3D global placement                    | 24 |

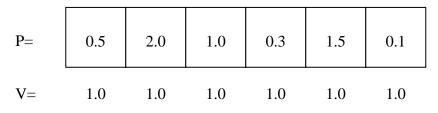

| Figure 7. Series of containers at various pressures.                               | 29 |

| Figure 8. Series of containers after pressure equalization                         | 29 |

| Figure 9. Pressure equalization with pressure reduction limit at 1.0.              | 29 |

| Figure 10. Pressure equalization toward 1.0 with damping                           | 30 |

| Figure 11. Cell shifting bin width versus density.                                 | 30 |

| Figure 12. Bin width versus density for the improved cell shifting method          | 31 |

| Figure 13. Row of cells in the x direction                                         | 32 |

| Figure 14. Local move procedure                                                    | 35 |

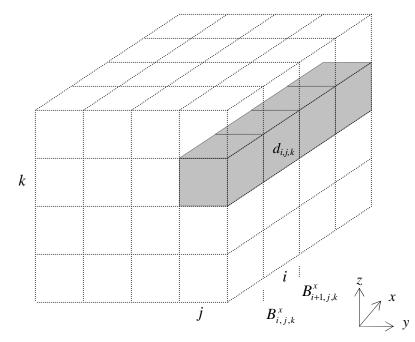

| Figure 15. Target region constructor                                               | 37 |

| Figure 16. Cell cost function constructor                                          | 38 |

| Figure 17. Bounding box algorithm for net <i>j</i> excluding cell <i>i</i>         | 38 |

| Figure 18. Region span determination.                                              | 39 |

| Figure 19. Global move procedure                                                   | 40 |

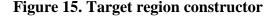

| Figure 20. Coarse Legalization Algorithm                                           | 40 |

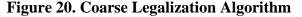

| Figure 21. xy-cross-section of density mesh showing external capacities            | 42 |

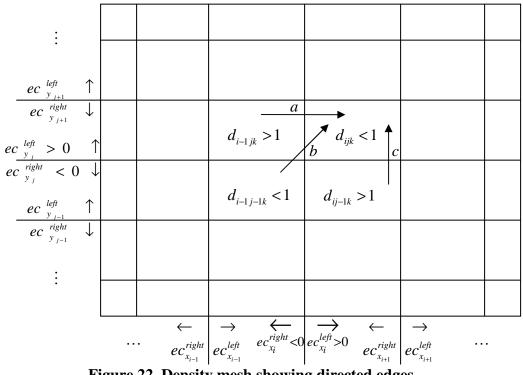

| Figure 22. Density mesh showing directed edges                                     | 43 |

| Figure 23. Target Region Expansion Algorithm                                       | 46 |

| Figure 24. Final Legalization Algorithm                                            | 47 |

| Figure 25. Post-Optimization Algorithm                                             | 48 |

| Figure 26. 3D Placement Method                                                     | 49 |

| Figure 27. Fast 3D Placement Method                                                | 51 |

| Figure 28. Slow 3D Placement Method                                                | 51 |

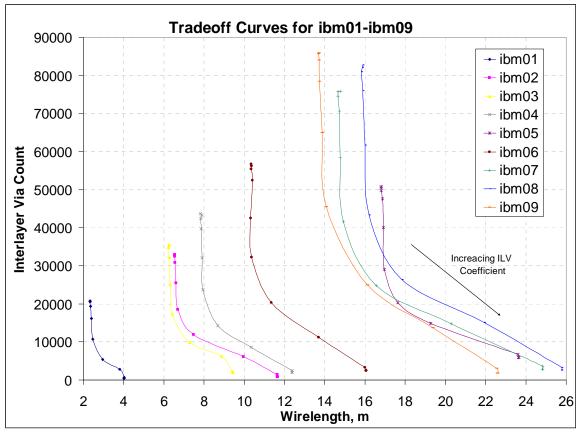

| Figure 29. Tradeoff between wirelength and interlayer via count for ibm01 to ibm09 | 52 |

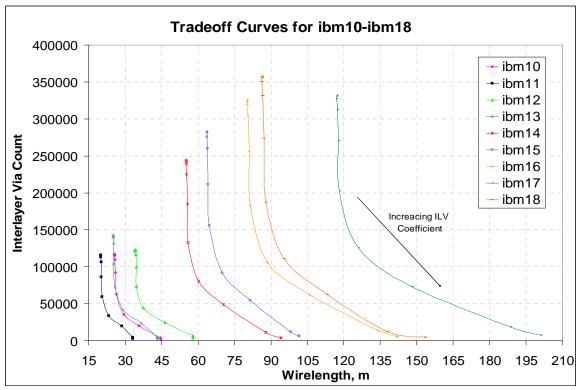

| Figure 30. Tradeoff between wirelength and interlayer via count for ibm10 to ibm18 | 53 |

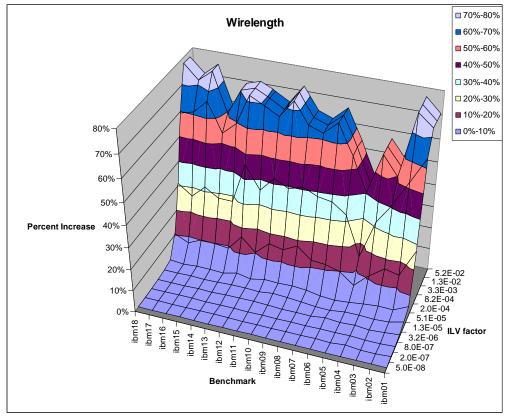

| Figure 31. | Percent increase in wirelength as $\alpha_{ILV}$ is increased for ibm01 to ibm18                                                     | 54 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------|----|

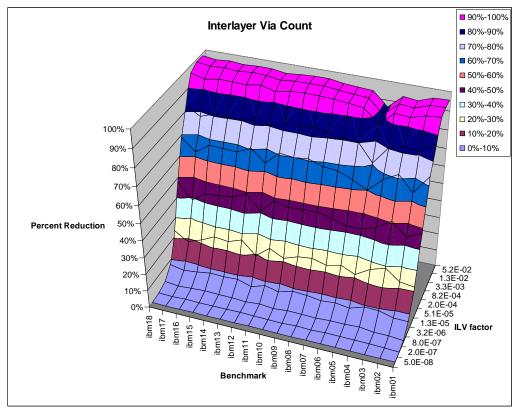

| Figure 32. | Percent reduction in interlayer via count as $\alpha_{ILV}$ is increased for ibm01 to ibm18                                          | 55 |

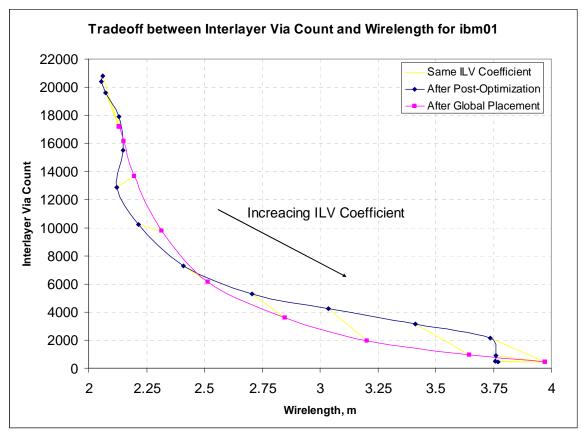

| Figure 33. | The tradeoff between interlayer via count and wirelength for ibm01                                                                   | 56 |

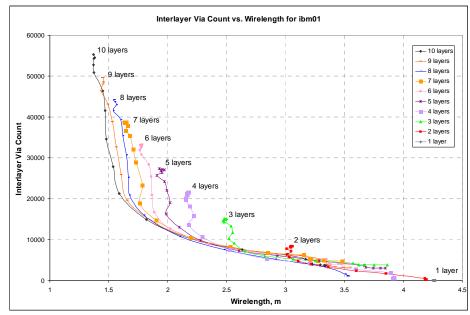

| Figure 34. | Tradeoff curves between wirelength and interlayer via counts as the number of layers is increased for ibm01.                         | 57 |

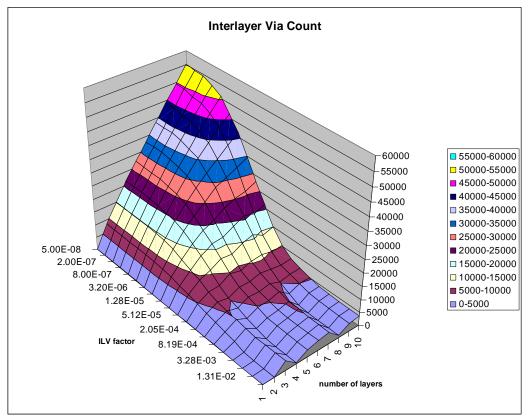

| Figure 35. | Interlayer via counts as $\alpha_{tLV}$ and the number of layers is varied for ibm01                                                 | 58 |

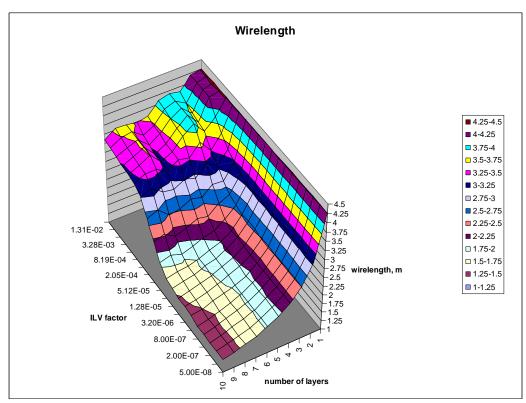

| Figure 36. | Wirelength as $\alpha_{LV}$ and the number of layers is varied for ibm01                                                             | 58 |

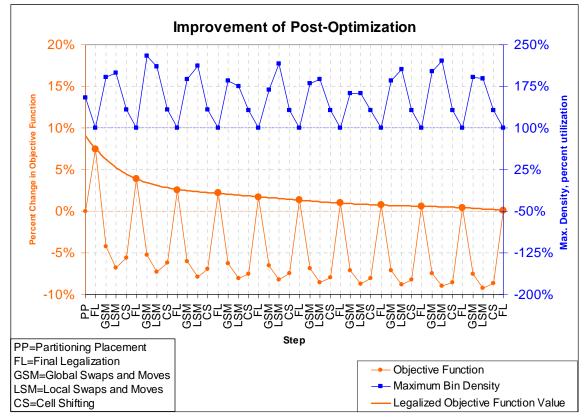

| Figure 37. | Improvement made by post-optimization on ibm01                                                                                       | 59 |

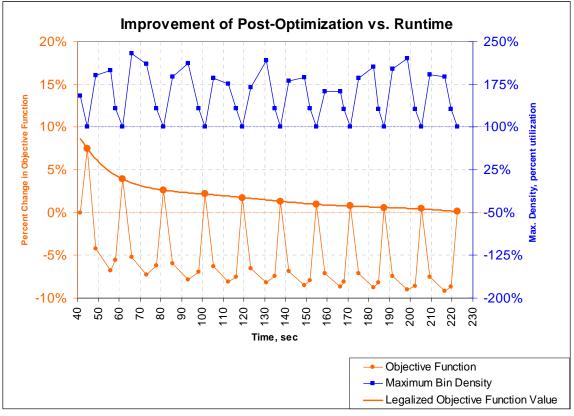

| Figure 38. | Runtime of post-optimization on ibm01                                                                                                | 60 |

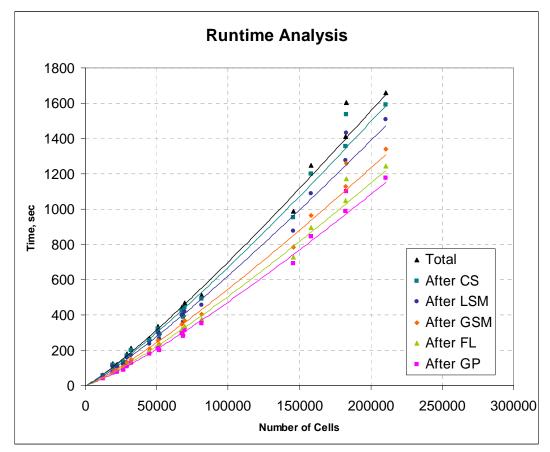

| Figure 39. | Runtime analysis of 3D placement                                                                                                     | 61 |

| Figure 40. | Thermal Resistance Approximation                                                                                                     | 67 |

| Figure 41. | Optimal arrangement of cells for net <i>i</i>                                                                                        | 72 |

| Figure 42. | Thermal Partitioning Placement                                                                                                       | 74 |

| Figure 43. | Thermal-Aware Legalization                                                                                                           | 75 |

| Figure 44. | 3D Thermal Placement Method                                                                                                          | 75 |

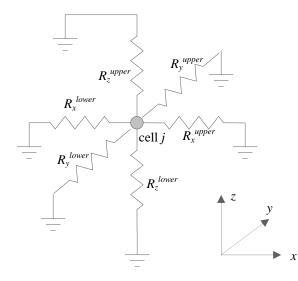

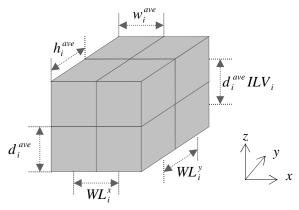

| Figure 45. | The effect of thermal placement on the average temperature of ibm01 as the thermal and interlayer via coefficients are varied.       | 81 |

| Figure 46. | The effect of thermal placement on the total power of ibm01 as the thermal and interlayer via coefficients are varied.               | 82 |

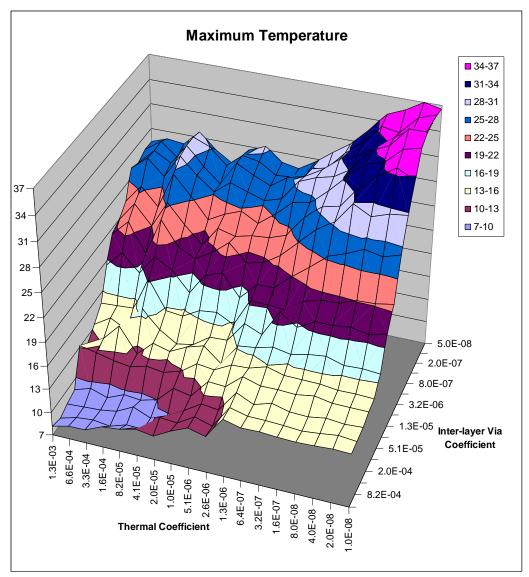

| Figure 47. | The effect of thermal placement on the maximum temperature of ibm01 as<br>the thermal and interlayer via coefficients are varied     | 83 |

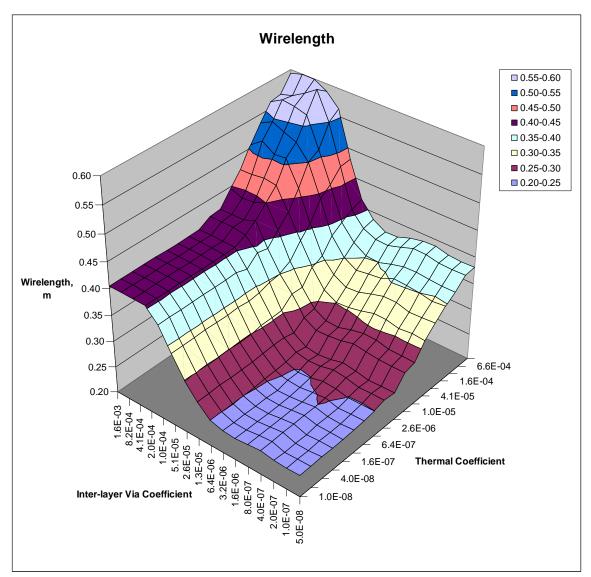

| Figure 48. | The effect of thermal placement on the wirelength of ibm01 as the thermal and interlayer via coefficients are varied.                | 84 |

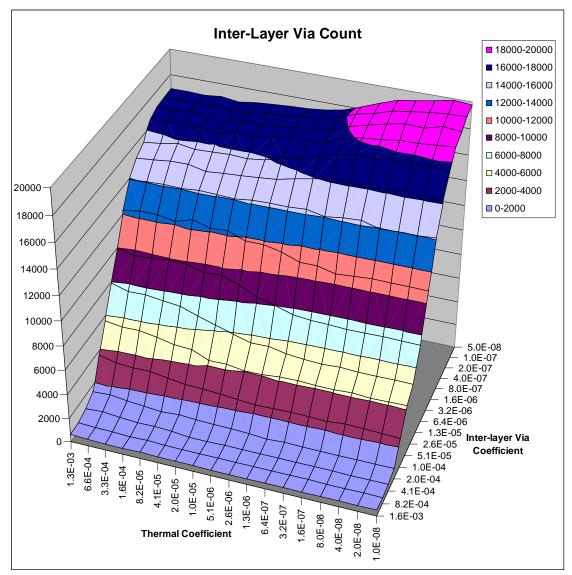

| Figure 49. | The effect of thermal placement on the interlayer via count of ibm01 as the thermal and interlayer via coefficients are varied       | 85 |

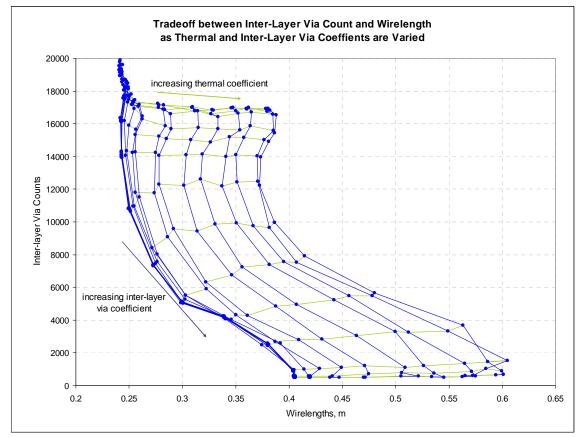

| Figure 50. | Tradeoff curves between interlayer via counts and wirelength as the thermal and interlayer via coefficients are varied.              | 86 |

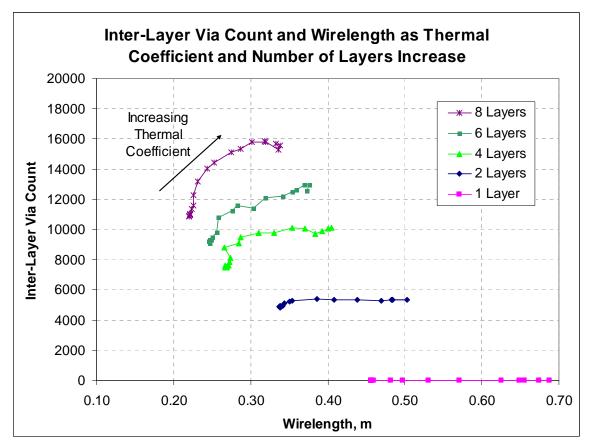

| Figure 51. | The effect of thermal placement on interlayer via count and wirelength as the number of layers is increased for ibm01                | 87 |

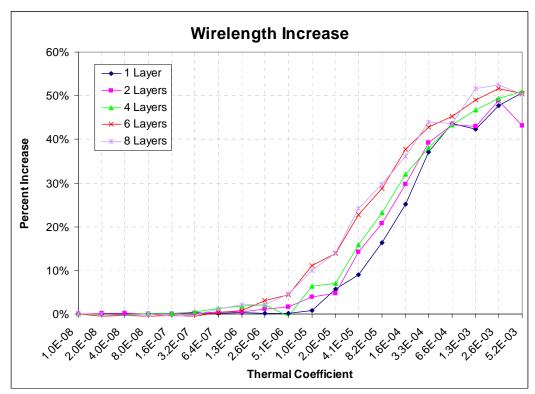

| Figure 52. | The percent increase in the wirelength of ibm01 as the thermal coefficient is increased with different numbers of layers.            | 88 |

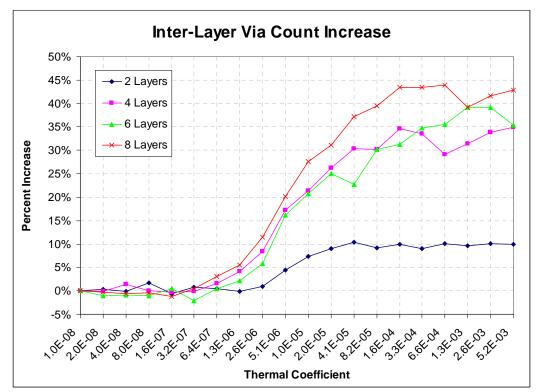

| Figure 53. | The percent increase in the interlayer via counts of ibm01 as the thermal coefficient is increased with different numbers of layers. | 88 |

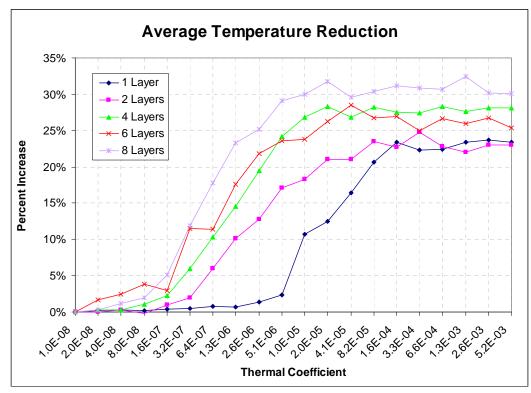

| Figure 54. | The percent reduction in the average temperature of ibm01 as the thermal                                                             |    |

|            | coefficient is increased with different numbers of layers                                                                                                                                           | .89  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

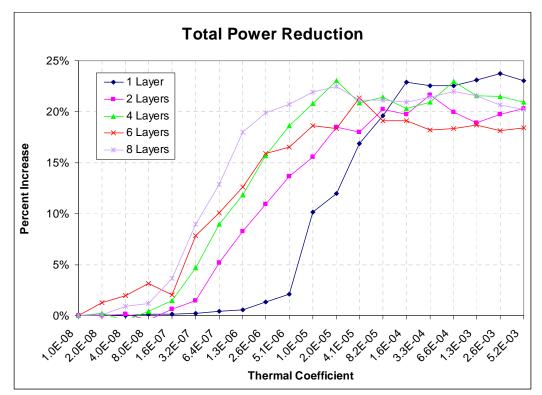

| Figure 55. | The percent reduction in the total power of ibm01 as the thermal coefficient is increased with different numbers of layers.                                                                         | .89  |

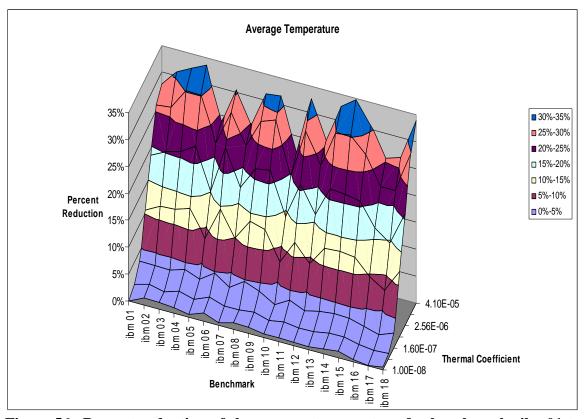

| Figure 56. | Percent reduction of the average temperature for benchmarks ibm01 to ibm18 as the thermal coefficient is increased.                                                                                 | .91  |

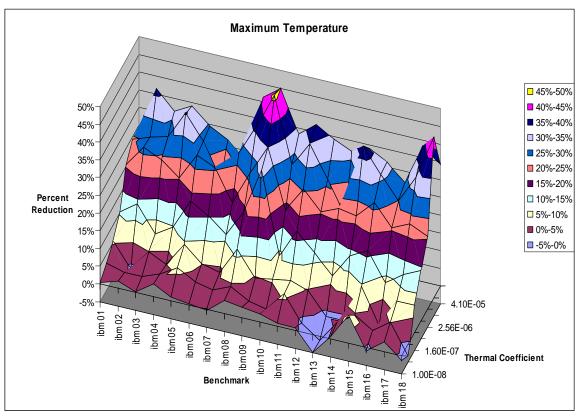

| Figure 57. | Percent reduction of the maximum temperature for benchmarks ibm01 to ibm18 as the thermal coefficient is increased.                                                                                 | .92  |

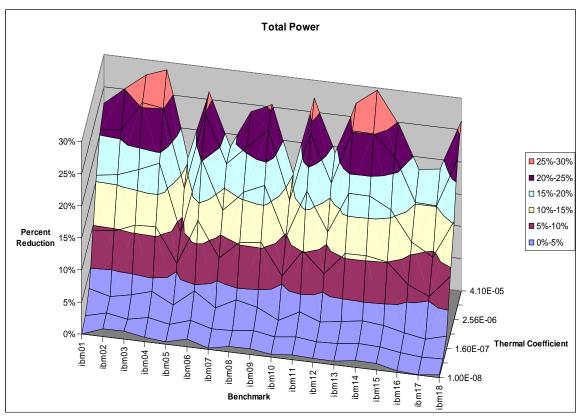

| Figure 58. | Percent reduction of the total power for benchmarks ibm01 to ibm18 as the thermal coefficient is increased                                                                                          | .93  |

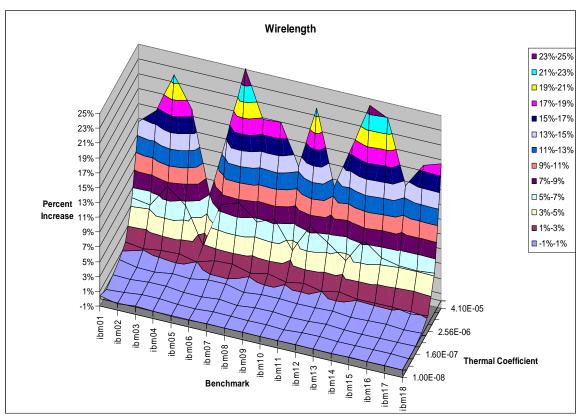

| Figure 59. | Percent increase in the wirelength for benchmarks ibm01 to ibm18 as the thermal coefficient is increased                                                                                            | .94  |

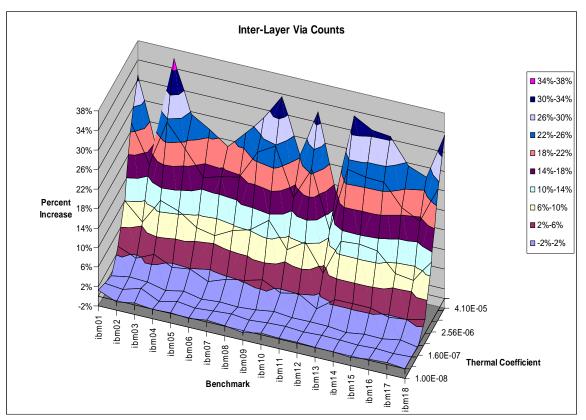

| Figure 60. | Percent increase in the interlayer via count for benchmarks ibm01 to ibm18 as the thermal coefficient is increased.                                                                                 | .95  |

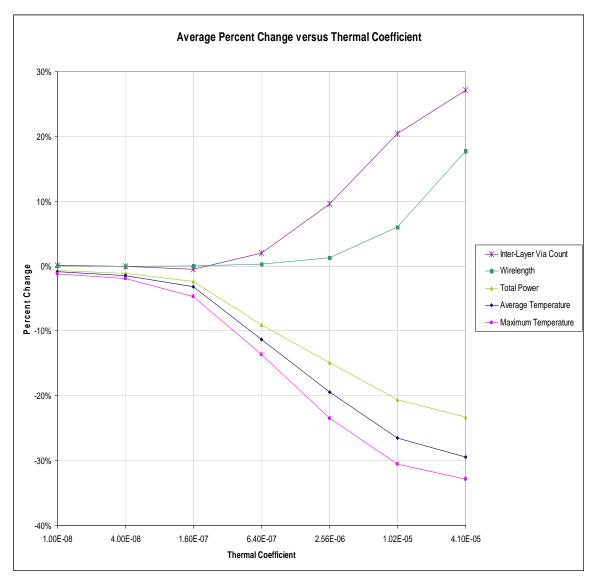

| Figure 61. | Average percent change in the interlayer via counts, wirelengths, total power, average temperatures, and maximum temperatures for benchmarks ibm01 to ibm18 as the thermal coefficients are varied. | .96  |

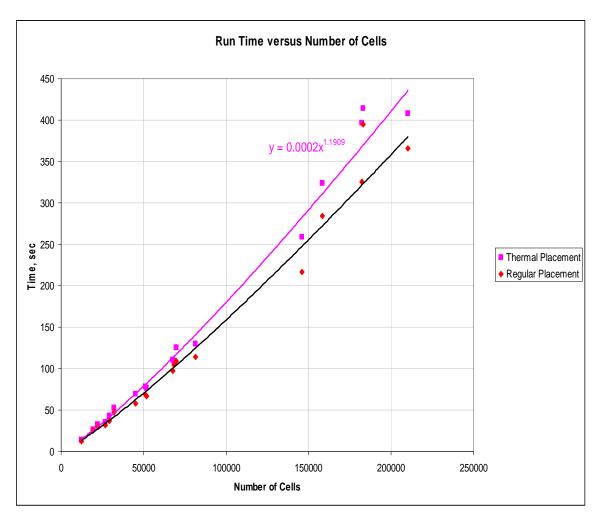

| Figure 62. | Runtime of thermal placement method.                                                                                                                                                                | .97  |

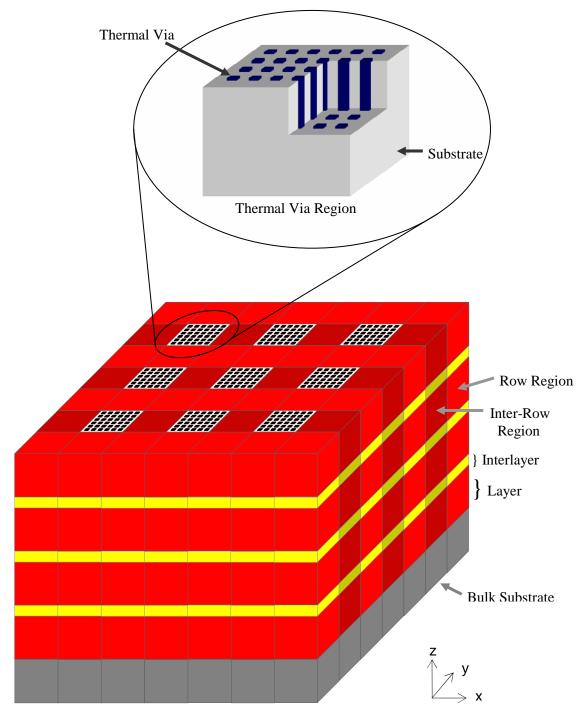

| Figure 63. | Thermal mesh for a 3D IC with thermal via regions.                                                                                                                                                  | .103 |

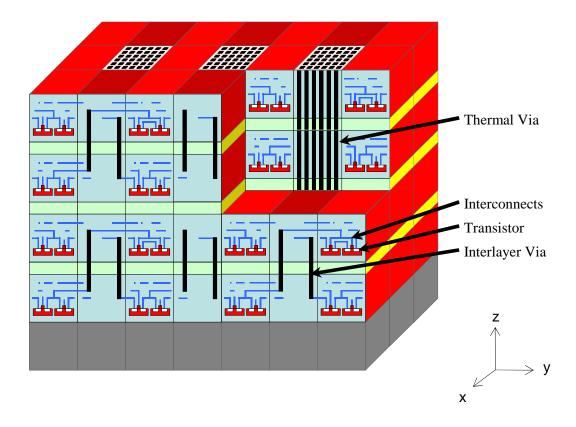

| Figure 64. | Cutaway showing transistors and interconnects.                                                                                                                                                      | .104 |

| Figure 65. | Percentage of thermal vias vs. thermal conductivity.                                                                                                                                                | .111 |

| Figure 66. | Pseudocode of the thermal via placement algorithm                                                                                                                                                   | .112 |

| Figure 67. | Thermal gradient optimization curves for struct.                                                                                                                                                    | .118 |

| Figure 68. | Temperature optimization curves for struct                                                                                                                                                          | .120 |

| Figure 69. | Maximum thermal via densities for struct                                                                                                                                                            | .122 |

| Figure 70. | Run Time Efficiency of our Method.                                                                                                                                                                  | .125 |

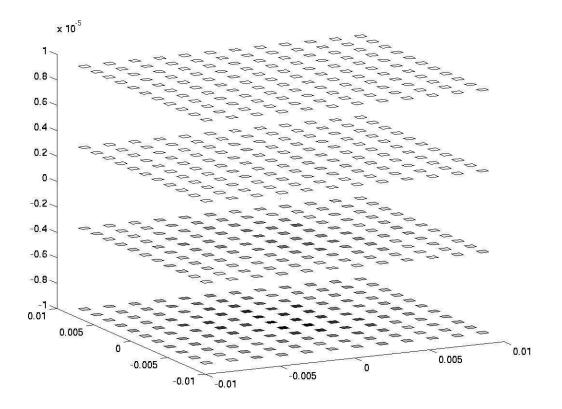

| Figure 71. | The thermal profile of struct before thermal via placement.                                                                                                                                         | .127 |

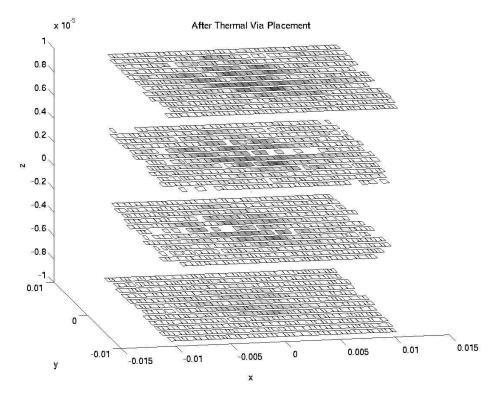

| Figure 72. | The thermal profile of struct after thermal via placement.                                                                                                                                          | .127 |

| Figure 73. | Thermal vias regions of struct after thermal via placement                                                                                                                                          | .128 |

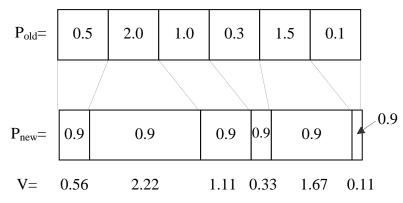

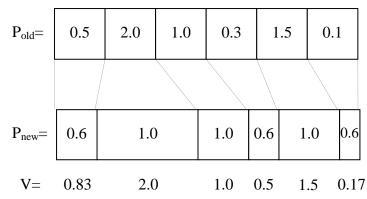

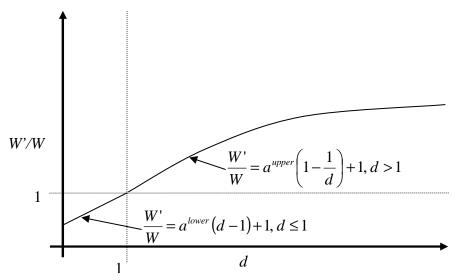

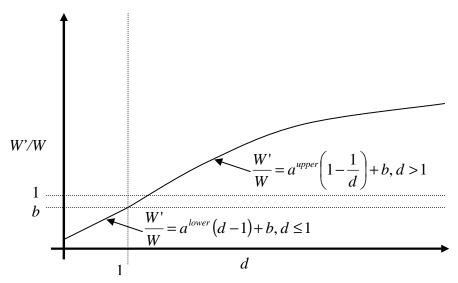

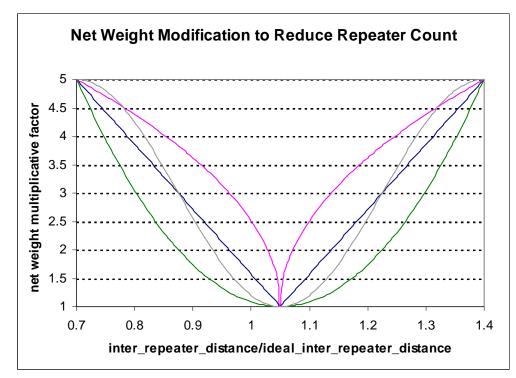

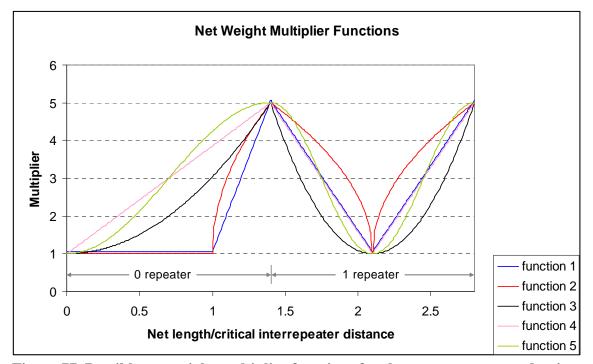

| Figure 74. | Possible net weight multiplier functions for repeater count reduction                                                                                                                               | .135 |

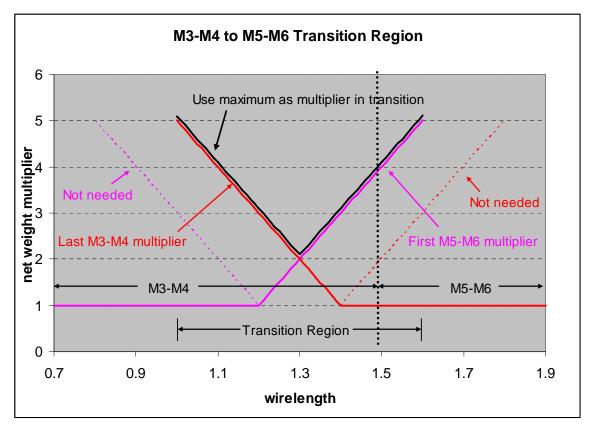

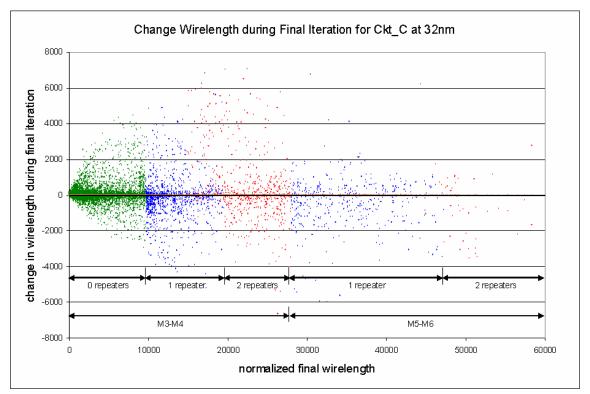

| Figure 75. | Overlapping M3-M4 deletion and M5-M6 insertion curve                                                                                                                                                | .137 |

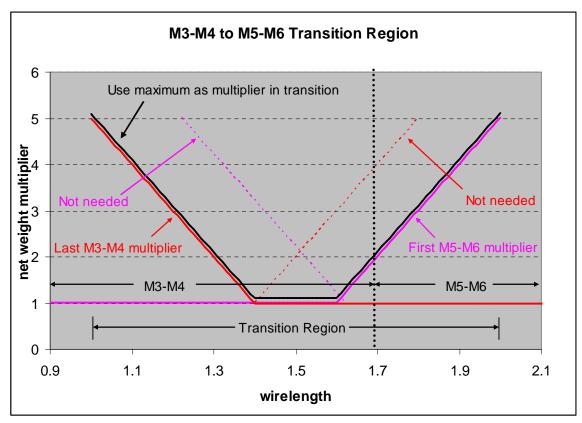

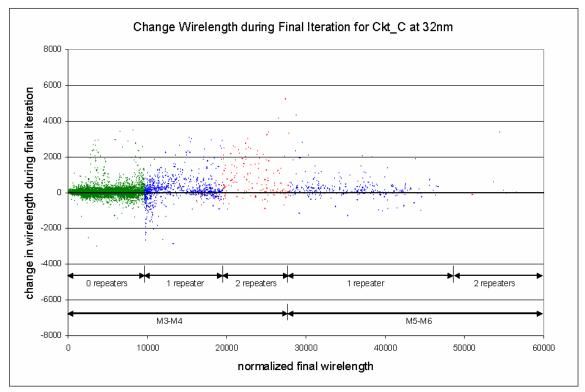

| Figure 76. | Overlapping M3-M4 insertion and M5-M6 deletion                                                                                                                                                      | .138 |